#### CHAPTER 27

# DETECTION AND AUTOMATIC VOLUME CONTROL

## BY B. SANDEL, A.S.T.C.

| Section               |        |     |       |     |          |         | Page |

|-----------------------|--------|-----|-------|-----|----------|---------|------|

| 1. A-M Detectors      |        |     | • • • | ••• | X.*/*X*X | • • •   | 1072 |

| 2. F-M Detectors      |        | ••• |       | *** | • •      | (* * *) | 1088 |

| 3. Automatic Volume C | ontrol |     |       |     |          | •••     | 1105 |

| 4. Muting (Q.A.V.C.)  | •••    | *** | •••   | ••• | • • •    |         | 1125 |

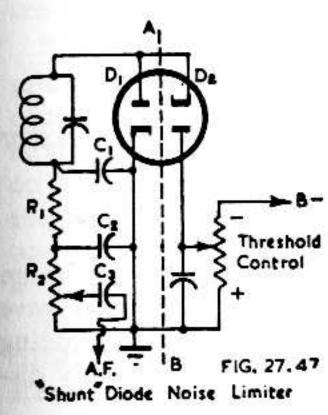

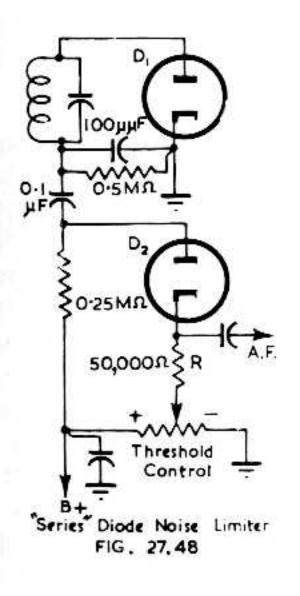

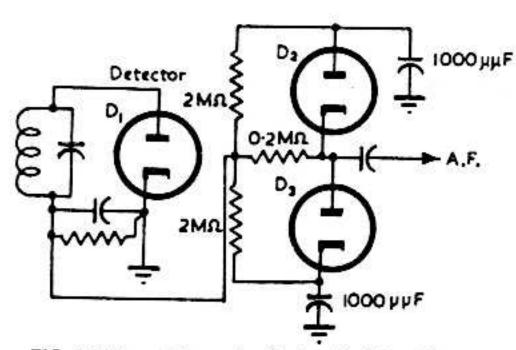

| 5. Noise Limiting     |        | ••• | •••   |     | •••      |         | 1130 |

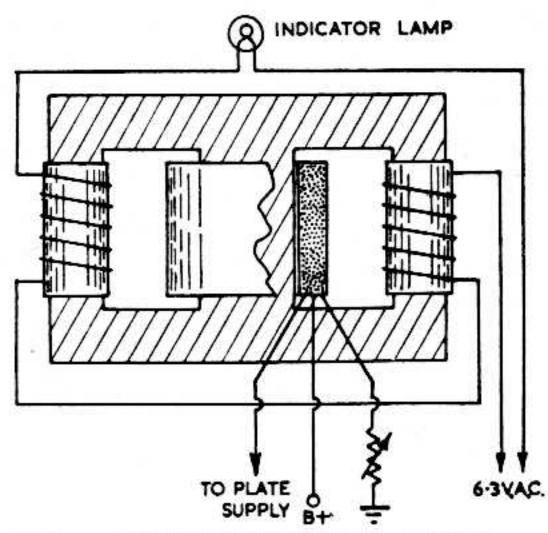

| 6. Tuning Indicators  |        | *** |       | ••• | • • •    | ***     | 1132 |

| 7. Crystal Detectors  |        | ••• | •••   |     | ***      |         | 1136 |

| 8. References         |        |     |       |     |          | •••     | 1138 |

## SECTION 1: A-M DETECTORS

(i) Diodes (A) General (B) Diode curves (C) Quantitative design data (D) Miscellaneous data (ii) Other forms of detectors (A) Grid detection (B) Power grid detection (C) Plate detection (D) Reflex detection (E) Regenerative detectors (F) Superregenerative detectors.

# (i) Diodes

(A) General

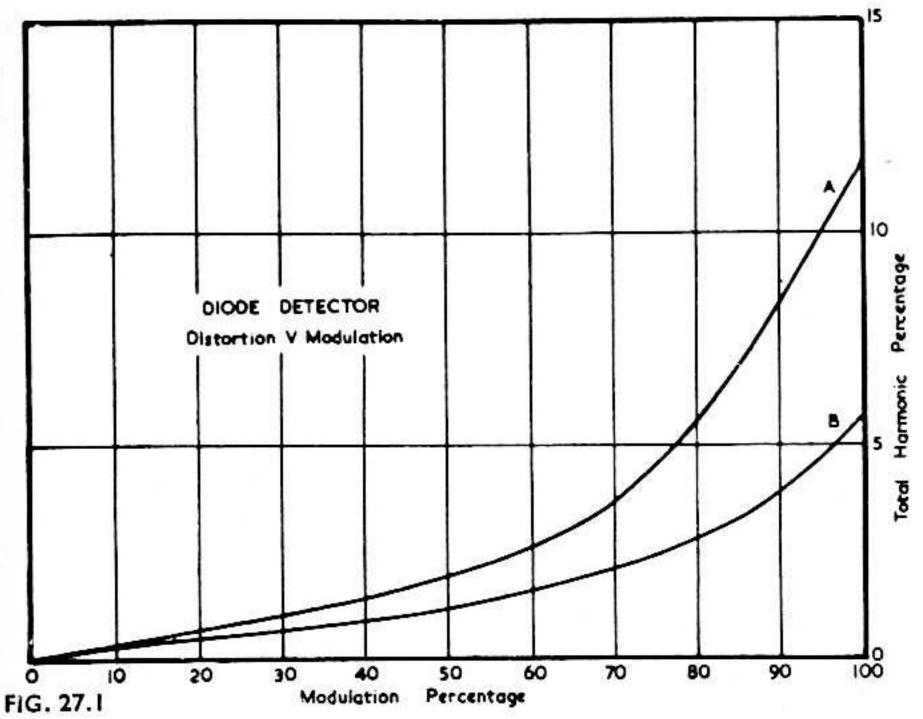

A diode has two electrodes namely plate and cathode. It is therefore identical in structure with a power rectifier but the term is generally restricted to valves which are used for detection or a.v.c. as distinct from rectifiers which are used for power supply. The operation of diodes with a.v.c. is considered in detail in Sect. 3 of this chapter. The operation of a diode on a modulated wave is rather different from the operation of a power rectifier, and it is necessary to consider the characteristic curves of a diode valve if a full understanding of the operation is to be obtained. The operation of diodes on a modulated input is considered in (B) below. Fig. 27.1 shows typical distortion curves for a diode operating firstly under ideal conditions with no a.c. shunting (curve B) and secondly the distortion resulting when a load of 1 megohm is shunted across a diode load resistance of 0.5 megohm (curve A). The respective percentages of harmonic distortion at 100% modulation are approximately 6% and 12% so that the presence of such shunting has a very marked effect on performance; these curves apply only for the particular conditions under which they were derived.

The design of a diode detector for low distortion is based on the following require-

ments:

(1) That the input voltage should not be less than 10 volts peak.

(2) That no appreciable a.c. shunting should be present.

The first of these two requirements is easily met for local stations and a voltage from 10 to 20 volts is quite common in receivers fitted with a.v.c. The second requirement is one which is difficult to satisfy. Shunting of the diode load may be due to:

- (1) The a.v.c. system.

- (2) The following grid resistor.

- (3) An electron ray tuning indicator.

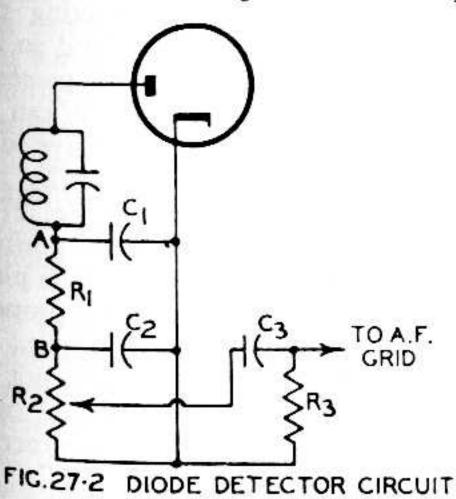

The circuit of a typical diode detector is shown in Fig. 27.2 in which the diode load resistance is  $R_2$  together with  $R_1$ ; the latter, in conjunction with  $C_1$  and  $C_2$ , form a r-f filter so that the r-f voltage passed on to the a-f system may be a minimum.  $R_1$  is generally made about 10% of  $R_2$  and typical values are 50 000 ohms and 0.5 megohm. The capacitances of  $C_1$  and  $C_2$  depend upon the frequency of the carrier; for an intermediate frequency of 455 Kc/s they may both be 100  $\mu\mu$ F.

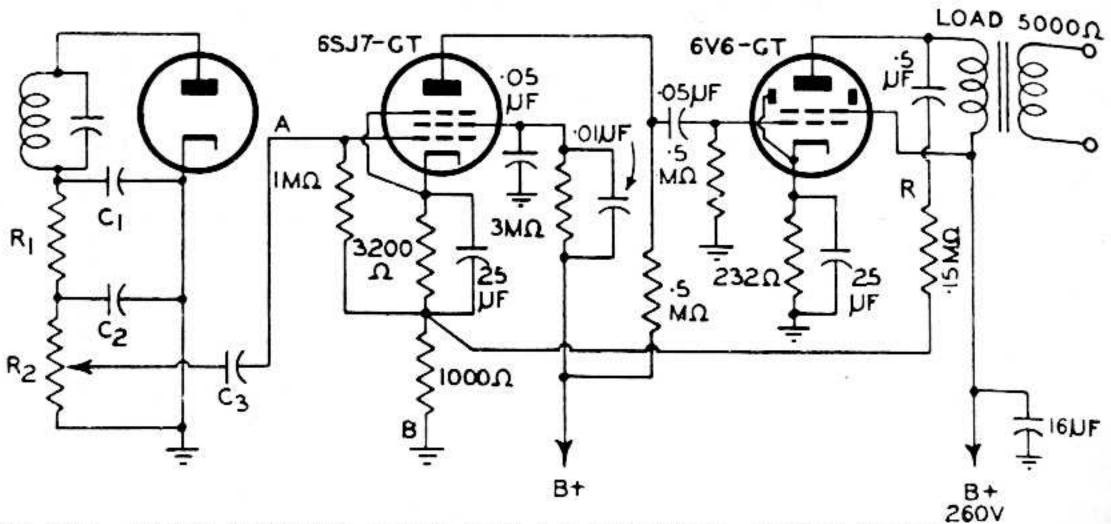

If the volume control  $(R_2)$  is turned to maximum the shunting effect due to  $R_3$  will be appreciable, since  $R_3$  cannot exceed 1 or 2 megohms with most types of valves. If, however, grid leak bias is used on a high-mu triode valve,  $R_3$  may be approximately 10 megohms and the input resistance of the valve will then be of the order of 5 megohms. This is sufficiently high to be unimportant but for lower values of  $R_3$  the distortion with the control set near maximum may be severe. It is found in most conventional receivers that the a-f gain is considerably higher than that required for strong carrier voltages and under these conditions the control will be turned to a low setting. The a.c. shunting effect due to  $R_3$  is practically negligible provided the control is below one-fifth of the maximum position. A good method of overcoming the a.c. shunting due to the audio amplifier is shown in Fig. 27.3. The diode may be in the same envelope as the i-f amplifier valve. Negative feedback is applied across

part of the cathode bias resistor for the a-f voltage amplifier valve. For the component values shown, the measured input resistance between points A and B is in excess of 10 megohms for frequencies up to about 10 Kc/s. A possible disadvantage is the reduction in overall gain because of the negative feedback, although this is not generally serious. Increasing the feedback resistance R increases the overall gain, but reduces the input resistance. Intermediate values of gain and input resistance may be selected as desired. For further details of receivers using this arrangement see Refs. 6 and 7.

FIG. 27-3 AUDIO AMPLIFIER GIVING LOW A.C. SHUNTING ACROSS DIODE LOAD.

Another useful method of reducing a.c. shunting effects is to use a cathode follower stage between the detector and the a-f voltage amplifier. This is often conveniently accomplished by employing a double triode valve, one section serving as the cathode follower and the other as an a-f voltage amplifier.

Distortion due to the a.v.c. system will be discussed in detail in Sect. 3 below. One type of distortion often encountered is caused by delayed a.v.c. systems at the point where the a.v.c. diode just starts to conduct. This form of distortion is called differential distortion and may be kept to low values by making the delay voltage small. The conventional arrangement for obtaining a.v.c. voltage from the primary of the last i-f transformer is generally preferred, as it reduces the a.c. shunting effect across the detector diode circuit.

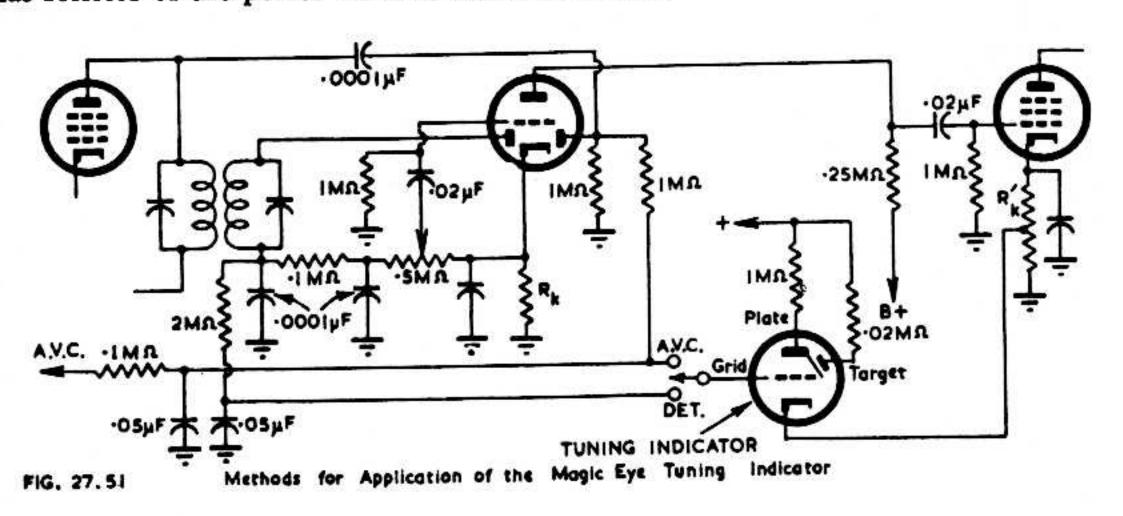

The a.c. shunting due to the addition of an electron ray tuning indicator to the diode detector circuit is serious and difficult to avoid. In order to reduce the distortion to a minimum the resistor feeding the grid of the tuning indicator may be made 2 megohms and the effect will only then be apparent at high percentages of modulation. If the tuning indicator is connected to the a.v.c. system it will not operate at low carrier levels unless the delay voltage is extremely small. One possible method, where the utmost fidelity is required, is to use the same circuit as for delayed a.v.c. but with a delay voltage of zero, and to connect the tuning indicator to this a.v.c. circuit. With this arrangement a.c. shunting due to the a.v.c. circuit and the tuning indicator is

eliminated, while differential loading no longer occurs.

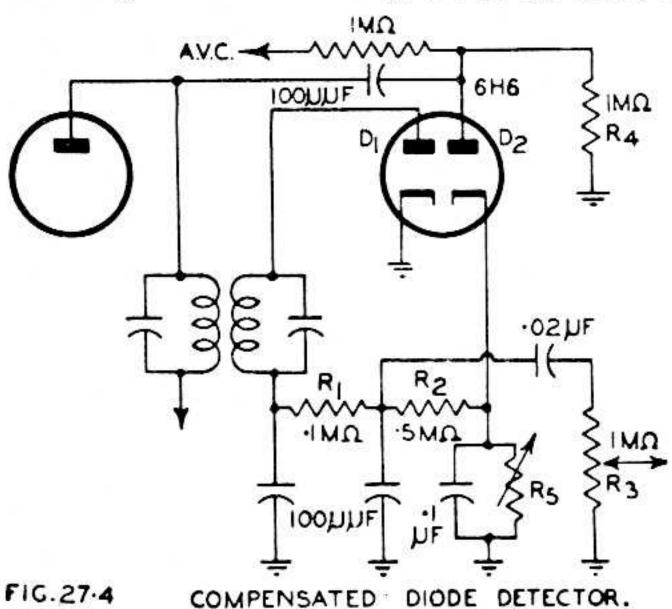

An interesting arrangement (Ref. 8) for counteracting the effect of a.c. loading, and so increasing the maximum percentage of modulation which can be handled without excessive distortion is accomplished by the use of the circuit of Fig. 27.4. In this arrangement a positive bias is applied to the diode plate in such a way as to be proportional to the carrier input. A fixed positive bias would not be satisfactory since it would only give low distortion at one carrier level.

#### (B) Diode curves

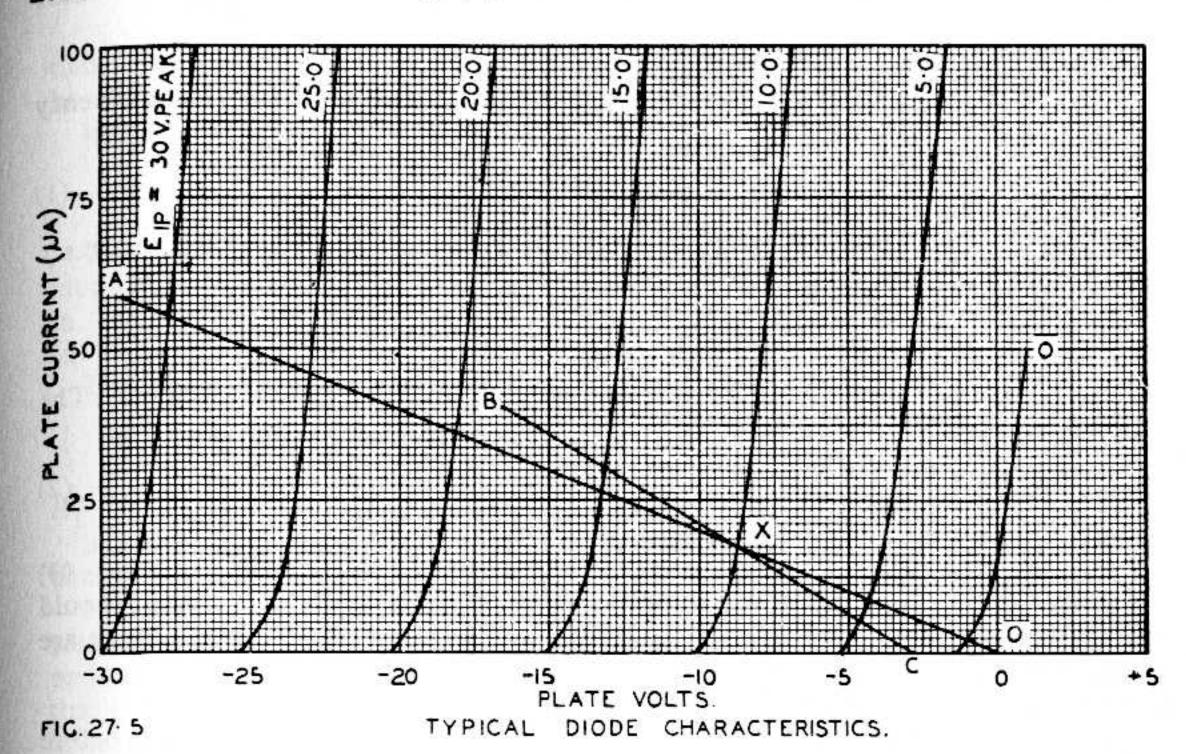

Typical diode characteristics are shown in Fig. 27.5. Each curve corresponds to the peak voltage of a constant unmodulated carrier voltage. On this graph may be drawn loadlines corresponding to diode load resistances in a similar manner as for triodes. The intersection of the applied loadline (OA) with the peak input voltage curve indicates the d.c. voltage developed by the diode and available for a.v.c. As the load resistance increases, so the d.c. voltage approaches the peak input voltage.

For example, if the carrier input is 10 volts peak and the diode load resistor 0.5 megohm, the diode current will be 17  $\mu$ A, and the d.c. voltage —8.7 volts. If 100% modulation is applied to the carrier, the operating point will move at audio frequency along the loadline from the intersection with the "0" curve, through X to the intersection with the 20 volt curve. The distortion over this excursion is small (about 5% second harmonic) and may be reduced still further by operating with a higher carrier input voltage.

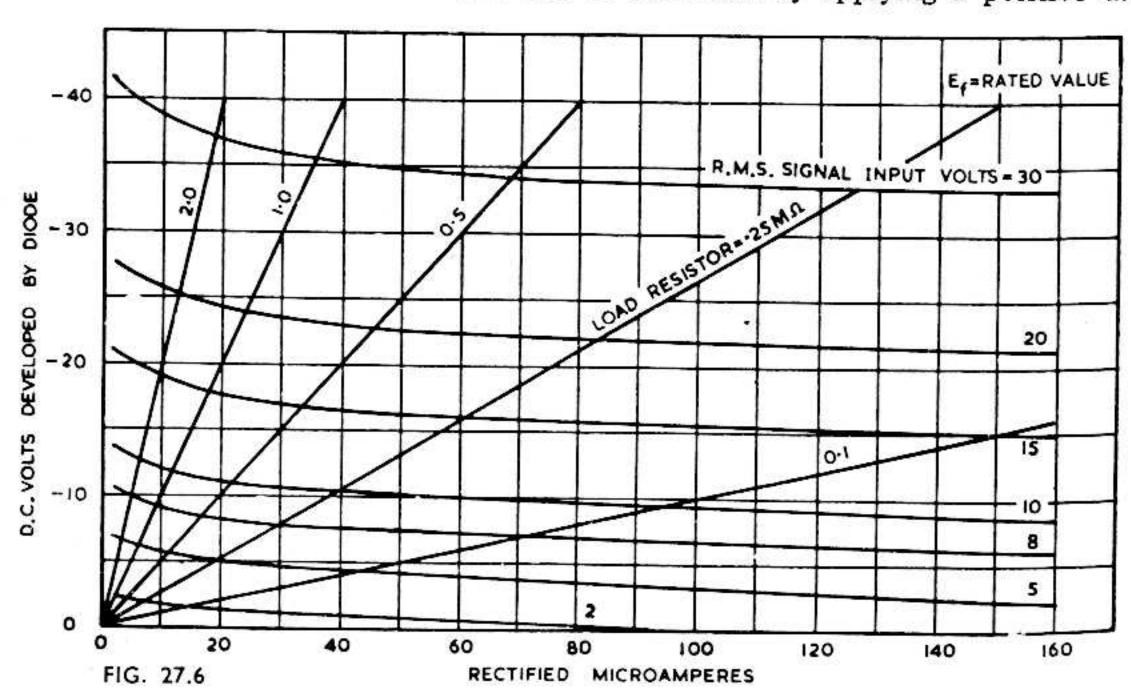

Typical diode curves with loadlines already drawn are shown in valve data books. Average curves are shown in Fig. 27.6 and these are applicable to the diodes incorporated in standard types of Radiotron diode-triode and diode-pentode valves. It has become the usual practice to show the signal input voltages in r.m.s. values rather than the peak voltages indicated in Fig. 27.5.

If the d.c. load resistance of 0.5 megohm, represented by OA in Fig. 27.5, is shunted by an a.c. load (such as would occur due to the grid resistor of the following valve) the dynamic loadline will be similar to BC, which passes through the static point X but which has a slope corresponding to the total effective a.c. load resistance. This loadline (BC) reaches cut-off at about 75% modulation and the distortion at higher percentages of modulation will consequently be severe. For any combination of d.c. and a.c. loads it is possible to draw the loadlines and determine the limiting percentage of modulation before distortion becomes excessive. It should not be overlooked that there will be some distortion present even before the limiting percentage of modulation is reached. The evaluation of this distortion is discussed below.

#### (C) Quantitative design data

Design formulae will be set out below so that the performance of the diode detector circuit can be assessed. These expressions are used in conjunction with the diode curves of Fig. 27.6. The design procedures are necessarily a series of compromises but the results form a useful practical guide. For a more detailed discussion the reader is referred particularly to Ref. 1 (p. 339), Ref. 2 (p. 413) and Ref. 5 (p. 553).

## (a) Diode detection efficiency

This can be found from curves such as those shown in Fig. 27.6. The efficiency (assuming a sine wave input) is

$$\eta = \frac{E_{dc}}{\sqrt{2E_{\tau m s}}}.$$

(1)

Suppose the d.c. load is 0.5 megohm and the signal input  $(E_{rms})$  is 15 volts (r.m.s.). Then from the curves  $E_{dc} = 16.8$  volts.

$$\eta = \frac{16.8}{\sqrt{2} \times 15} = 0.793 \text{ or } 79.3\%.$$

Actually the a.c. load should be determined and used for all calculations. The a.c. load is, from Fig. 27.2,

$$R_{ac} = R_1 + \frac{R_2 R_3}{R_2 + R_3} \tag{2}$$

The d.c. load for the diode detector is

$$R_{dc} = R_1 + R_2. \tag{3}$$

If simple a.v.c. is used the effect of additional a.c. shunting due to this circuit should be taken into account. In this case the effects of additional capacitive reactance are usually neglected for simplicity.

#### (b) Critical modulation ratio

The highest percentage of modulation which can be handled by the detector, before serious distortion of the modulation envelope occurs, is given by

$$m = 1 - \eta F \frac{R_{dc}}{R_{dc} + R_3/F} \tag{4}$$

where F = fraction of  $R_{dc}$  across which  $R_3$  is tapped

$$= \frac{R_2}{R_1 + R_2} = \frac{R_2}{R_{dc}}.$$

If  $R_{dc}=0.5~\text{M}\Omega$ , made up from  $R_1=50~000~\Omega$  and  $R_2=0.45~\text{M}\Omega$ , then F=0.45/0.5=0.9. Taking  $\eta=0.793$  as before, and  $R_3=1~\text{M}\Omega$  we have,

$$m = 1 - 0.793 \times 0.9 \frac{0.5}{0.5 + 1/0.9} = 0.78 \text{ or } 78\%.$$

It should be noted that the smaller F is made, the higher the critical modulation ratio. If F is fixed, then  $R_3$  is made as large as possible but is usually limited to about 1 or 2 megohms unless special circuit arrangements, such as those discussed previously, are made.

The critical modulation ratio can also be increased by applying a positive d.c.

bias voltage to the diode plate. This arrangement is only satisfactory if the bias can be changed for each i-f input voltage  $(E_{rms})$  see Ref. 1 (page 348).

For this case

$$m = \left(\frac{\sqrt{2}E_{rms} + E_{bias}}{\sqrt{2}E_{rms}}\right) \left(1 - \eta F \frac{R_{dc}}{R_{dc} + R_3/F}\right)$$

(5)

The circuit of Fig. 27.4 shows a practical arrangement for increasing the critical modulation ratio by applying positive bias to the diode plate, as mentioned previously in Sect. (A) above.

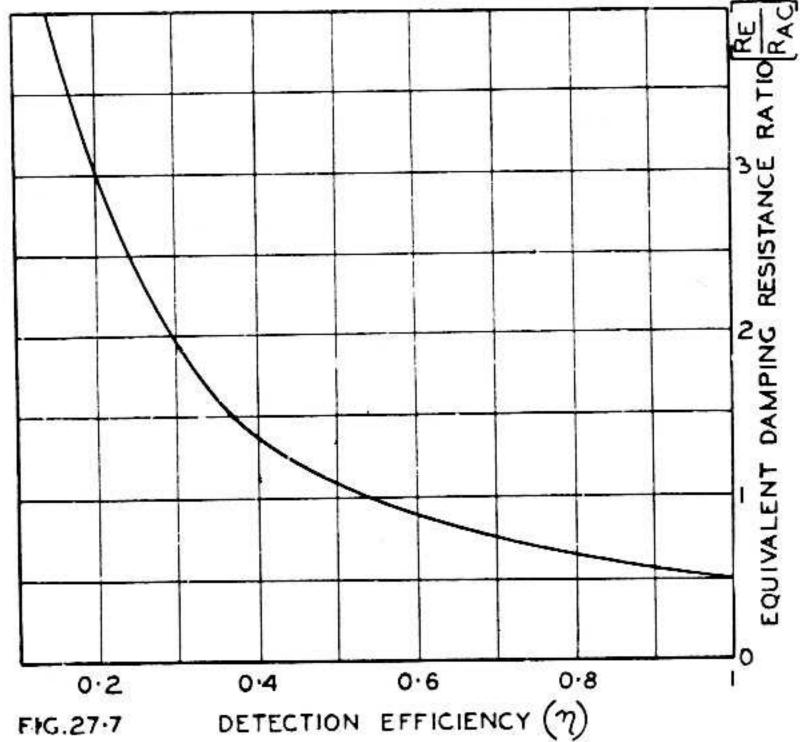

(c) Equivalent damping across i-f transformer

The secondary circuit damping is found approximately from

$$R_E = \frac{R_{ac}(\sqrt{1 - \eta^2} - \eta \cos^{-1}\eta)}{\eta(\cos^{-1}\eta - \eta\sqrt{1 - \eta^2})}.$$

(6)

$R_E/R_{ac}$  can be read directly from Fig. 27.7 for various values of  $\eta$ .

Suppose  $R_{ac} = 0.36 \text{ M}\Omega$  and  $\eta = 0.793$  then, since  $R_E/R_{ac} = 0.7$ , the equivalent

damping resistance is  $R_E = 0.7 \times 0.36 = 0.25 \text{ M}\Omega$ .

It is often taken in practice (as a "rule of thumb") that the equivalent damping resistance is half the d.c. diode load resistance. This gives an equivalent damping resistance of  $R_{dc}/2 = 0.5/2 = 0.25 \,\mathrm{M}\Omega$  in this case. However, it should be realized that if the diode efficiency is taken as unity, the equivalent damping resistance which appears across the tuned circuit is half the a.c. load resistance; this is indicated by Fig. 27.7.

Damping of the i-f transformer primary is serious when the a.v.c. voltage is derived from a diode detector connected to this voltage source. The usual arrangement is a capacitor (100  $\mu\mu$ F or less) taken from the plate connection of the transformer primary to the diode plate. The additional primary damping from this source is approximately one third of the d.c. load resistance for the a.v.c. diode. This also follows fairly readily if it is considered that  $R_{dc}$  shunts the primary of the transformer, and in addition the diode conduction current also adds damping equivalent to a parallel resistance of approximately  $R_{dc}/2$ . From this

$$R_E = \frac{R_{dc}(R_{dc}/2)}{R_{dc} + R_{dc}/2} = \frac{R_{dc}}{3}.$$

For a typical case, the a.v.c. resistance would be 1 megohm, and so the equivalent damping resistance would be approximately 0.33 megohm. If the i-f amplifier valve

has a plate resistance of 0.8 megohm the primary damping resistance would be 0.23 megohm.

This means that, with detector and a.v.c. diodes conducting, both the secondary and primary circuits of the i-f transformer are heavily damped and this damping must be taken into account when the i-f transformer, connected between the last i-f voltage amplifier valve and the diode detector, is being designed. Delayed a.v.c. will, of course, affect the primary circuit damping and three conditions arise: the diode not conducting, the diode just starting to conduct, and the diode conducting when the applied voltage is reasonably large. When conduction just starts the damping depends very largely on the diode detection efficiency and will vary quite appreciably for a small range of input voltages. It is usually sufficient, however, to know the tuned circuit damping for the two conditions, diode not conducting, and diode conducting with a reasonably large input voltage. For the diode not conducting the added damping is approximately  $R_{ac}$ ;  $R_{dc}$  should not be used here. With the diode conducting the added damping can be taken as  $R_{dc}/3$  with sufficient accuracy in some cases since in this case the fact that the diode detection efficiency is not unity offsets to some extent the increase in damping which is obtained when Rac is used in place of  $R_{dc}$ .

Damping of the transformer tuned circuits as determined above assumes linear diode plate-voltage—plate-current characteristics. For parabolic diode detection the damping differs by only a small amount from that given by the linear characteristics and so, in practice, it is seldom necessary to treat the two cases separately. In any case the order of accuracy to be expected in the final results from the procedures set out, would hardly justify any additional refinements in the design calculations.

### (d) The actual degree of modulation

The degree of modulation applied to the detector is always less than the modulation of the incoming carrier. The actual value of m which the detector will be required to handle is given approximately by

$$m = m' \frac{R_3(R_{dc} + 2Z_L)}{R_{dc}R_3 + 2Z_L(R_{dc} + R_3)}$$

$$m' = \text{original modulation are stated}$$

(7)

where m' = original modulation percentage

$R_{dc} = R_1 + R_2$  (see Fig. 27.2)

$R_3$  = grid resistor of following stage (see Fig. 27.2)

and  $Z_L$  = load impedance presented to the i-f voltage amplifier preceding the detector stage; including the effects of all damping on the primary and secondary of the i-f transformer.

In addition, at higher audio frequencies the reduction of side band amplitude by the selectivity of the earlier stages in the receiver results in a further decrease in depth of modulation.

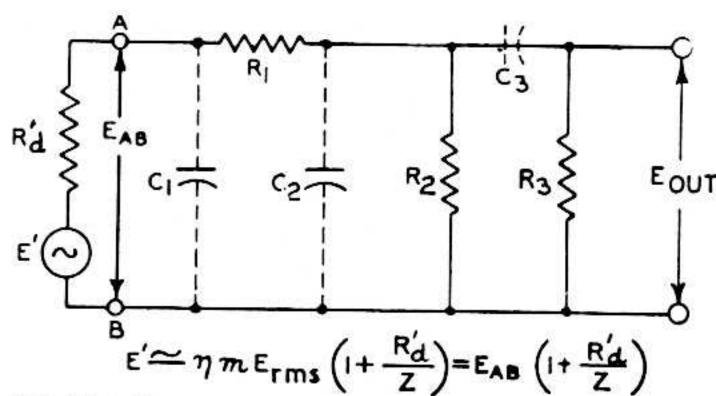

## (e) Audio frequency output voltage and response (frequency distortion)

The approximate r.m.s. audio frequency output voltage can be determined for a particular arrangement by using the equivalent circuit of Fig. 27.8. It is often assumed that all capacitive reactances are negligible, for simplicity in carrying out gain calculations. However, the circuit is readily modified to include  $C_1$ ,  $C_2$  and  $C_3$  as

FIG. 27-8 EQUIVALENT DIODE CIRCUIT AT AUDIO

shown by the dotted lines, and any additional capacitances in the circuit can be included if necessary. For this diagram

m =modulation factor

$E_{rms} = i-f \text{ input voltage}$

$\eta$  = detection efficiency determined from curves of Fig. 27.6

Z = total load impedance connected between the terminals AB. (This is equal to  $R_{ac}$  over the middle audio frequency range)

$$R_{ac} = R_1 + \frac{R_2 R_3}{R_2 + R_3}$$

and  $R'_d$  = internal equivalent resistance of diode at audio frequencies. This is given by the inverse slope of the curves of Fig. 27.6.

$R_1$ ,  $R_2$  and  $R_3$  are as shown in Fig. 27.2.

It should be noted that  $R'_d$  is not the diode conduction resistance  $(R_d)$  but is related to it by

$$R'_{d} = \frac{\pi R_{d}}{\cos^{-1}\eta} \,. \tag{8}$$

Also  $R'_d$  and  $R_d$  are not constant for all operating conditions. For our previous example we see from the 15 volt (r.m.s.) curve of Fig. 27.6, and taking the diode load as being

$$R_1 + R_2 = 0.5 \text{ M}\Omega$$

, for simplicity,

$R'_d = \frac{(17 - 16.5) \times 10^6}{(42 - 26)} = 31\ 200 \ \Omega$ .

It will be seen that  $R'_d$  is determined in a rather similar manner to that used for finding the plate resistance of multi-element valves. The diode conduction resistance in this case is (approximately) 6500 ohms.

It is sometimes required to find the audio frequency response and this can readily be determined from the complete circuit of Fig. 27.8. A suitable procedure would be as for r.c. amplifiers in which the capacitances are ignored over the middle frequency range (say around 400 to  $3000 \, \text{c/s}$ ), and the audio voltage output is calculated for the resistance network only. At low frequencies the effects of  $C_1$  and  $C_2$  can be ignored since they are usually about 50 to  $100 \, \mu\mu\text{F}$  each, and only the effect of  $C_3$  would be considered. At high frequencies  $C_3$  would be neglected and the effects of  $C_1$  and  $C_2$  considered. Often only the maximum output voltage is required plus the total output variation from say 50 c/s to  $10 \, \text{Kc/s}$ , and this simplifies the calculations. If Fig. 27.8 is inspected it will be seen that it is a simple matter to apply the generalized low frequency response curves given in Chapter 12. The high frequency curves can also be applied directly if  $C_1$  can be neglected (this is usually permissible) and  $C_1$  and  $C_2$  are considered as being in parallel.

When using the circuit of Fig. 27.8 it is more convenient to determine the voltage  $E_{AB}$  since this is given directly by

$E_{AB} = \eta m E_{rms}$ . It follows that, over the middle frequency range,

$$E_{out} = E_{AB} \left( rac{R_{ac} - R_1}{R_{ac}}

ight)$$

and  $rac{E_{out}}{E'} = rac{E_{out}}{E_{AB}} imes rac{E_{AB}}{E'} = rac{R_{ac} - R_1}{R_{ac} + R_d}$ .

If  $R_1$  can be neglected in comparison with  $R_2$  and  $R_3$  in parallel, then  $E_{out} = E_{AB}$  over the middle frequency range.

It is more accurate to determine  $E_{AB}$  from the curves of Fig. 27.6, since  $\eta$  is not constant for a modulated carrier voltage and the effects of contact potential are included in the measured data. The procedure is to draw the a.c. loadline on the graph and note the d.c. voltages  $E_{dc_1}$  and  $E_{dc_2}$  given by the maximum and minimum values of  $E_{rms}$  during modulation. From this

$$E_{AB} = \frac{1}{2\sqrt{2}} (E_{dc_1} - E_{dc_2}).$$

The simplified graphical procedure is only suitable when the amplitudes of harmonics higher than the second are negligible [see also (h) below]. More accurate graphical methods are required if this is not true.

To compare the results obtained by the two methods, assume  $E_{rms} = 15$  volts and the percentage modulation is 50% (i.e. m = 0.5). As determined previously  $\eta = 0.793$ , and it will be taken that  $R_{ac} = R_{dc} = 0.5$  megohm. Then

$E_{AB} = \eta m E_{rms} = 0.793 \times 0.5 \times 15 = 5.95$  volts (r.m.s.). From Fig. 27.6,  $E_{dc1} = 26.5$  volts and  $E_{dc2} = 7.5$  volts so that

$$E_{AB} = \frac{1}{2\sqrt{2}} (26.5 - 7.5) = 6.7 \text{ volts.}$$

The discrepancy between these two results is easily explained, as an examination of typical diode circuits giving the d.c. voltage developed by the diode in the absence of signal input shows that there is about -0.5 to -1 volt developed across a diode load of 0.5 megohm. This difference is also illustrated by the curve of Fig. 27.5, which shows that -1 volt is developed for the conditions being considered. It is also seen that the variation in detection efficiency  $(\eta)$  over the range of voltage used does not have a large effect on the final result. The presence of d.c. voltage across the load resistor, in the absence of signal input voltage, is due to contact potential in the diode.

(f) Effect of shunt capacitance on detection efficiency

Too low a value for  $C_1$  and  $C_2$  will affect the detection efficiency. Provided the **total** shunt capacitance across the diode load is not less than  $\frac{12.72}{fR_{ac}}$   $\mu\mu$ F the effect can be neglected where

f= frequency (expressed in Mc/s)  $R_{ac}=R_1+rac{R_2R_3}{R_2+R_3}$  (expressed in M $\Omega$ ).

For our previous example of  $R_{ac}=0.36~\mathrm{M}\Omega$ , and i-f of 455 Kc/s, the capacitance due to  $C_1$  and  $C_2$  should not be less than about 78  $\mu\mu$ F; this includes all stray capacitances. In the circuit of Fig. 27.2 typical values of  $C_1$  and  $C_2$  are 100  $\mu\mu$ F each and if  $R_1$  is neglected it is seen that the total capacitance is more than twice the value required even when strays are neglected. It would be feasible to reduce  $C_1$  and  $C_2$  to 50  $\mu\mu$ F respectively with a reduction in attenuation at the higher audio frequencies: (g) Non-linear distortion

If the value of total capacitance across the diode load resistance is too large, the discharge time constant will be too long and the voltage across the diode load will not follow the modulation envelope. This will give rise to non-linear distortion and suggests that the rate of discharge of the load circuit should not be less than the maximum rate of change of the modulation envelope. It can be shown that non-linear a-f distortion due to this cause can be almost completely avoided provided that

$$\frac{1}{\omega C_t R_{dv}} \gg m. \tag{9}$$

Suppose we neglect the decoupling resistance  $(R_1)$  in Fig. 27.2, as this unnecessarily complicates calculations when its value is about 1/10 of  $R_2$  (the usual case).

What is required, is to determine a value for  $C_t R_{dc}$  which will allow m = 1, i.e. the incoming signal to be 100% modulated. However, it should be clear from previous discussion that the modulation percentage is generally a good deal lower than this figure, and it seldom happens that very high modulation percentages occur at high audio frequencies.

Take  $R_{dc}$  as 0.5 megohm, then  $1/\omega C_t = mR_{dc} = 1 \times 0.5 \times 10^6$ .

Assume that the highest audio frequency is 10 Kc/s, then  $\omega = 2\pi \times 10^4$  and so

$$C_t = \frac{10^{12}}{2\pi \times 10^2 \times 0.5 \times 10^2} = 31.8 \ \mu \mu F.$$

This is the largest value  $C_t$  should have if the detector is to be capable of handling audio frequencies of 10 Kc/s and 100% amplitude modulation.

It will be noticed from (e) above that the detector efficiency will be reduced if  $C_i$  is

given the value determined. A suitable practical compromise would be to make  $C_1 = C_2 = 50~\mu\mu\text{F}$  and retain the values of  $R_1$ ,  $R_2$  and  $R_3$  given in the example. If improved decoupling is required then  $R_1$  could be increased to say 0.1 megohm. This also permits a higher critical modulation ratio at the expense of some reduction in available audio output. The difficulty with non-linear distortion is not encountered when  $C_t$  is charging, since the diode is conducting and the charging time constant is approximately  $C_t R'_d$  which in our example is, taking  $C_t = 100~\mu\mu\text{F}$ ,  $100 \times 10^{-12} \times 3.12 \times 10^4 = 3.12~\mu$  secs. The discharge time constant is approximately  $100 \times 10^{-12} \times 0.5 \times 10^6 = 50~\mu$  secs.

# (h) Estimate of magnitude of non-linear distortion

The distortion can be found from the curves of Fig. 27.6 in the same way as for power amplifiers (Ref. 3, p. 100). The operating point corresponding to a given signal input is marked on the a.c. loadline. The maximum and minimum excursions of the modulation envelope are now marked on this same line. If only second harmonic distortion is required (and higher order harmonic distortion is very small) these points are sufficient. For distortion calculations which involve harmonics higher than the second the methods detailed in Chapter 13 should be used. The expression to be used here is

2nd harmonic percentage

$$=\frac{1}{2}\left(\frac{A-1}{A+1}\right)\times 100\%$$

, (10)

where  $A = \frac{\text{positive current swing}}{\text{negative current swing}}$

Voltage swing would give the same results, since the load is taken as being a pure resistance.

Suppose we take  $R_{ac}=R_{dc}$  and use the 0.5 M $\Omega$  loadline. The carrier input voltage is 15 volts (r.m.s.) and is modulated 50%. The voltage swing is thus  $\pm$  7.5 volts (r.m.s.) about 15 volts.

From Fig. 27.6 this gives (approximately)

$$A = \frac{53 - 33.5}{33.5 - 16} = 1.11$$

2nd harmonic percentage  $=\frac{1}{2}\left(\frac{0.11}{2.11}\right)\times 100 = 2.6.$

The true a.c. loadline would indicate somewhat more distortion than is given by this simple example.

## (D) Miscellaneous data

(a) With radio receivers using diode-triode or diode-pentode valves as combined detectors and a-f or i-f amplifiers several effects require consideration. Where the combined valve is used in the a-f application, difficulty is often experienced with residual volume effect ("play-through"). This effect is quite distinct from the minimum volume effect experienced with receivers using a reflexed amplifier. The residual volume is heard in the receiver output when the audio volume control is turned to zero (the grid may also be earthed as a further check). The cause of the effect is capacitive and electronic coupling between the detector diode and the plate of the a-f voltage amplifier.

In some cases there may be direct coupling at audio frequencies, but usually the important factor is coupling of modulated i-f currents which are detected in the audio amplifier.

A complete cure for the trouble is to combine the detector diode with the i-f voltage amplifier. However, this can sometimes lead to difficulties with regeneration or degeneration at i-f due to coupling between the detector diode and signal grid. When the valve is retained as an a-f amplifier it is necessary to keep all stray coupling to a minimum by careful layout and wiring. Diode pentodes are often helpful, particularly when series screen feed is used, as adequate screen by-passing gives a marked improvement. Adequate cathode circuit by-passing is essential in all cases. Neutralization to reduce the effect is almost useless unless rather elaborate circuits are used. In some cases different types of sockets offer an improvement. If simple a.v.c. is used,

earthing, or even leaving disconnected, the second diode will often effect an almost complete cure. Obviously the diode connection nearest the plate of the voltage amplifier is the one which should be earthed.

A second effect which is less frequently encountered is residual volume due to capacitance between a diode and the control grid of a combined detector and a-f amplifier. Normally this capacitance is unimportant because with the volume control turned right down the control grid is grounded through the grid coupling capacitor (see Fig. 27.2). However if the audio amplifier is grid leak biased it may have a 10 megohm grid leak, and in this case a 0.001  $\mu$ F grid coupling capacitor would give adequate bass response for a small receiver. Under these conditions a voltage of the order of one thousandth of the i-f input to the diode could appear on the control grid and with a high gain receiver this is ample to give annoying minimum volume. The remedy, of course, is to increase the size of the grid coupling capacitor.

(b) In general, diodes do not start to conduct at precisely the point where the plate voltage exceeds zero. Contact potentials and other effects will sometimes allow the valve to conduct when the diode plate voltage is slightly negative (this is usual with valves having indirectly heated cathodes), but in other cases (e.g. some battery valves) conduction does not occur until the plate voltage is appreciably positive. This point can be appreciated by an examination of typical diode curves. The effects of the contact potentials will be further considered in Sect. (3) below when automatic

volume control is being discussed.

For a discussion of the effects of positive and negative start of plate current (which may be deliberately introduced as mentioned in (C)(b) above) in diode detectors the

reader is referred to Ref. 1, Chapter 8.

(c) There are distinct advantages in having the **a-f volume control as the diode** load. For the usual operating conditions on local signals the setting of the control is fairly well down, and so the effects of a.c. loading are very much reduced. This advantage is lost when the control is in the grid circuit of the a-f voltage amplifier. The disadvantage is that many controls become noisy, usually after a fairly short period, when they have the diode current passing through them. A compromise arrangement may be best with the control in the grid circuit  $(R_3$  in Fig. 27.2) and  $R_1$  about 0.1 megohm and  $R_2$  say 0.5 megohm.

(d) As a summary of the characteristics of the diode detector, it may be stated that its performance as regards frequency and non-linear distortion is excellent provided the input voltage is high and the factors discussed above regarding a.c. shunting etc. are incorporated in the detector design. All forms of detectors suffer from distortion at low input levels, but the diode has the particular advantage that the input may be increased to a very high level with consequent reduction of distortion, without any

overloading effect such as occurs with other forms of detectors.

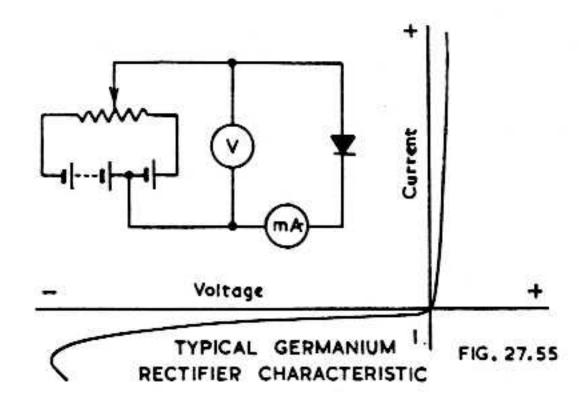

(e) Crystal diodes are described in Section 7.

## (ii) Other forms of detectors

(A) Grid detection

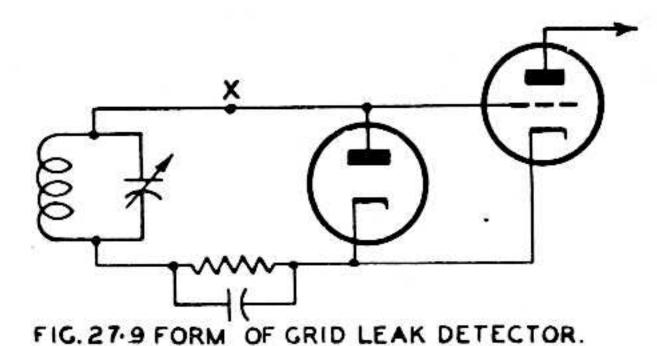

Leaky grid or "cumulative detection" has been used for many years and is still widely used for certain applications. The theory of its operation is essentially the same as that of the diode except that a triode is also used for amplification. The derivation of a leaky grid detector from the combination of a diode and triode is shown in Fig. 27.9. Whether the grid capacitor and resistor are inserted as

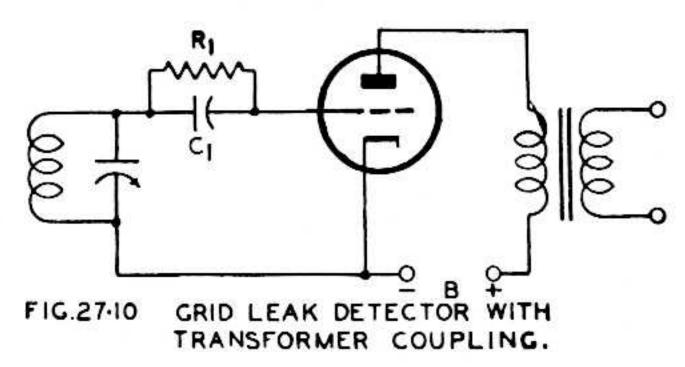

shown (as is usual with the diode) or at the point X is immaterial from the viewpoint of operation. The diode is directly coupled to the triode and therefore the audio frequency voltages developed in the diode detector are passed on to the triode grid, but at the same time this grid is given a d.c. bias through the d.c. voltage developed in a similar way to that by which a.v.c. is obtained. Consequently the operating point of the triode varies along the  $e_{\sigma}$ - $i_{\sigma}$  curve from zero towards more negative grid bias voltages as the carrier voltage is increased. This is the same effect as that obtained when the diode is omitted (Fig. 27.10) since the grid and cathode of the triode act as a diode and produce the same results. The illustration given was purely to demonstrate the derivation of the one from the other and not to be a practical form of detector since no advantage is gained by retaining the diode in the circuit.

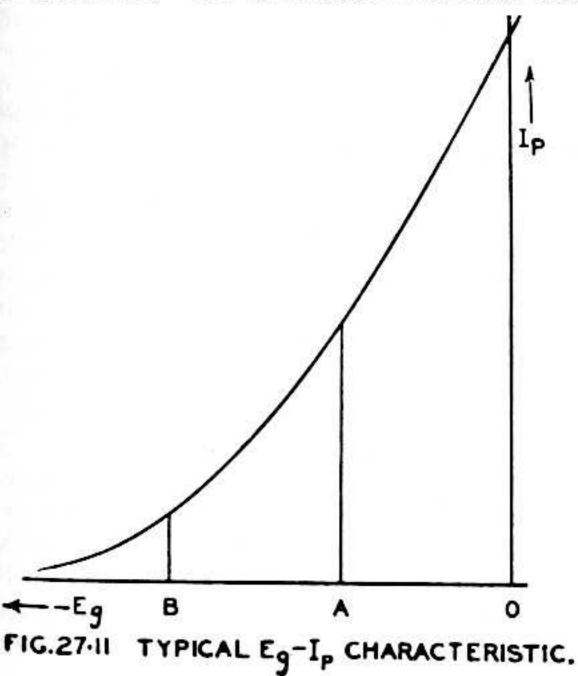

It will be seen that the operating point varies along the  $e_p$ - $i_p$  characteristic curve between zero bias and the cut-off point (Fig. 27.11). There will be a certain strength of carrier at which the detection will be most satisfactory, and at lower or higher levels detection will not be so satisfactory on account of improper operating conditions. If with a certain carrier input voltage the d.c. bias on the grid is OA, then the point corresponding to peak modulation is B where OB equals twice OA. If the point B is on the curved part of the characteristic, or in the extreme case actually beyond the cut-off, the distortion will be severe. A valve having low  $\mu$  and low  $g_m$  is capable of operating with a higher carrier voltage than a valve with improved characteristics, but the gain in the detector stage will be less. There is a further difficulty in that the plate current at no signal, or at very weak signal, may be excessively high. If transformer coupling is used this may, in extreme cases, damage the valve, or pass too much direct-current through the transformer, unless the plate supply voltage is reduced. If resistance coupling or parallel-feed is used the efficiency of the detector is decreased. As with diode detection there is distortion at low levels due to the

"diode characteristics" but as distinct from the diode, the overload point occurs at quite a low carrier voltage. This method of detection is therefore very much limited in application.

With battery type valves used as cumulative grid detectors it is often advantageous to connect  $R_1$  (Fig. 27.10) to filament positive;  $C_1$  remains as before. The advantage obtained is that larger modulation percentages can be handled and detection will start with smaller input voltages. The arrangement is equivalent to supplying the grid, which is acting as the plate of a diode, with a positive bias voltage (see Ref. 1, p. 357) and moving the position of the start of grid current.

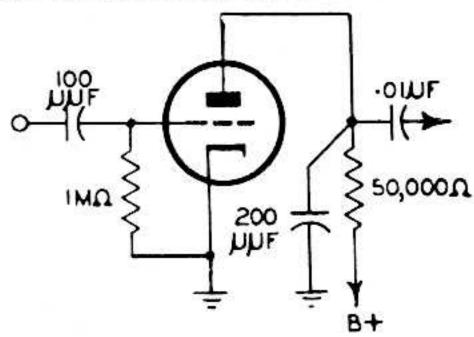

A typical circuit for a grid leak detector as used in radio receivers is shown in Fig. 27.12.

Damping of the input circuit occurs in the same manner as for a diode but additional damping occurs because of grid-plate coupling. The arrangement shown in Fig. 27.12 for the grid resistor further increases the loading on the input circuit. Detailed discussions of this type of circuit can be found in Refs. 2 (p. 414), 1 (p. 377) and 10.

FIG. 27-12 TYPICAL GRID LEAK DETECTOR WITH R-C COUPLING.

## (B) Power grid detection

Power grid detection is a modification of leaky grid or cumulative detection and the circuit is identical in form, but the operating conditions are so chosen that the valve will operate on higher carrier voltages without overloading. In order to obtain a short time constant from the grid capacitor and resistor combination the capacitance and resistance are reduced, thereby improving the high audio frequency response. Under optimum conditions the distortion is at least as high as that of a diode together with increased distortion due to the curvature of the  $e_g$ - $i_p$  characteristic. The overload point, even though higher than that of ordinary leaky grid detection is at a much lower level than that with diode detection.

All forms of grid detection, particularly "power grid detection," involve damping of the grid circuit due to grid current, and this damping causes loss of sensitivity and selectivity. Grid detection is thus similar to diode detection in that it damps the input circuit. It has the advantage over diode detection in that gain is obtained in the detector which can be still further increased if transformer coupling is used between it and the following stage. Transformer coupling can, of course, only be used when the valve has a low plate resistance.

The foregoing comparison between a diode and a grid detector is on the basis of the detector alone. In modern practice the diode detector is frequently in the same envelope with a voltage amplifier and the total gain is quite high.

#### (C) Plate detection

Plate detection or "anode bend detection" involves operation towards the point of plate current cut-off so that non-linearity occurs, thereby giving rectification. Owing to the slow rate of curvature the detection efficiency is small, but there is an advantage in that the amplification which is obtained makes up, to a certain extent, for the poor detection efficiency. Due to the gradual curvature the distortion is very great with low input voltages, and even with the maximum input before overload occurs the distortion is rather high with high percentages of modulation. An important advantage of plate detection is, however, that the grid input circuit is not damped to any great extent, and the detector is therefore sometimes spoken of as being of infinite impedance, although this term is not strictly correct.

With pentode valves it is possible to use either "Bottom Bend Rectification" as with triodes or "Top Bend Rectification" peculiar to pentodes. This "top bend" in resistance coupled pentode characteristics can be seen on valve data sheets e.g. type 6J7 dynamic  $e_g - i_p$  characteristics provide a good illustration (Fig. 12.14A).

A similar effect occurs with triodes, but only in the positive grid region, and for this reason it is incapable of being used for plate rectification. For top bend rectification with a pentode valve it is desirable to operate the valve with a plate current in the region

of 0.95  $(E_B/R_L)$ . The exact operating point for optimum conditions depends upon the input voltage.

Pentode valves are particularly valuable as plate detectors since the gain is of such a high order. If resistance coupling is used the gain is reduced very considerably, and in order to eliminate this loss it is usual to adopt choke coupling using a very high inductance choke in the plate circuit, shunted by a resistor to give a more uniform frequency response. If the shunt resistor were omitted the high frequencies would be much greater than the low frequencies in relative level.

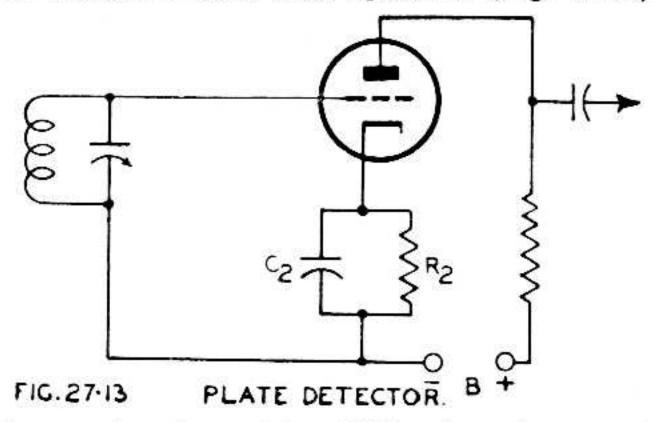

With all forms of plate detectors the bias is critical and since different valves of the same type require slightly different values of bias the use of fixed bias is not recommended. A very high value of cathode resistance is usually adopted to bias the valve very nearly to cut-off, and in such a way that if valves are changed, or vary during life, the operating point maintains itself near optimum (Fig. 27.13).

Screen grid and pentode valves with self-bias have been used as plate detectors very satisfactorily for a number of years, although the distortion with the usual arrangement is too high for them to be used in any but the cheapest radio receivers at the present time. Such a detector is, however, permissible for some types of short-wave reception and for amateur communication work where its high grid input impedance results in higher sensitivity and selectivity.

With the usual plate detector the cathode bypass capacitor ( $C_2$ , Fig. 27.13) has customarily been made sufficiently large to by-pass both audio and radio frequencies. Often  $C_2$  is a 25  $\mu$ F electrolytic in parallel with a 500  $\mu\mu$ F mica capacitor. This arrangement, although widely used in the past, is not a correct one and leads to distortion when the modulation factor is at all high. The effect is similar to that described in connection with diode detectors having the a.c. loadline appreciably different in slope from the d.c. loadline. The correct procedure calls for the resistor  $R_2$  to be by-passed for radio frequencies only, and although this results in a very considerable loss in gain because of negative feedback, the results obtainable are excellent. In a typical case  $R_2$  might be taken as 10 000 to 100 000 ohms and  $C_2$  as 500 to 100  $\mu\mu$ F respectively, the plate load resistor would be about 0.25 megohm; additional r-f decoupling is usual in the plate circuit, although this is not shown in Fig. 27.13. This circuit is often called a reflex detector, although this term is sometimes reserved for cases where 100% negative feedback is used with a plate detector, and the audio output is then taken from the resistor in the cathode circuit; the plate is earthed for a.c. in this case. The results obtainable from the modified plate detector are excellent, and are comparable with those given by the diode arrangement. The reflex detector is further discussed below.

#### (D) Reflex detector

The reflex detector is essentially a plate detector with negative feedback. Any amount of feedback may be applied from zero to 100%, and as the feedback increases, so the distortion decreases and the stage gain decreases until in the final condition with 100% feedback the gain is less than unity. The reflex detector has an even higher input impedance than the usual type of plate detector, and is therefore valuable in certain applications. Under certain conditions the input resistance is negative and can lead to instability troubles. The increased selectivity can also result in side-

band cutting. The degree of feedback may be adjusted to give any required gain (within reasonable limits) by altering the size of cathode by-pass capacitor and the relationship between the plate and cathode load resistance, but the distortion increases with gain and if low distortion is required the maximum gain is limited to about three or four times even with a pentode valve. With maximum degeneration and stable operating conditions, the distortion (see Ref. 11) is about the same as for a diode operating under similar input voltage conditions, while the reflex detector has the distinct advantage of high input impedance. One application which appears to be of importance is in high fidelity t.r.f. receivers, but even here the reflex detector has not shown any very marked improvement over the diode from a consideration of distortion alone. Input voltages in the order of 10 volts (r.m.s.) are usually most satisfactory when low distortion is desired and in a typical case using 100% feedback about 3% total harmonic distortion can be expected when the modulation depth approaches 100%. This assumes that the a.c. shunting is high (say 10:1 or so) compared with the d.c. load. Some useful discussion is given in Refs. 14 (pages 51-55) and 15. These performance figures can be compared with those stated previously for the diode detector under similar operating conditions. Reflex detectors do not provide a.v.c. and so are not used in normal broadcast receivers. They could be used in combination with amplified a.v.c. to provide a receiver with good characteristics.

Typical circuit component values have been discussed in (C) above in connection with modified plate detectors. For the case of 100% negative feedback (i.e. the load resistance is in the cathode circuit and the plate is earthed for a.c.) the cathode resistance is made large compared with  $1/g_m$  and a typical value is 25 000 ohms. The by-pass capacitance across this resistance can be about 500  $\mu\mu$ F. There is seldom any difficulty with a.c /d.c. ratios as the grid resistance of the following a-f stage is generally about 0.5 megohm. Additional components required are a blocking capacitor, to prevent the d.c. cathode voltage from being applied to the grid of the a-f amplifier, and a series resistor and shunt capacitor to provide additional r-f decoupling between the two circuits.

A limitation of the reflex detector is that there is a definite maximum for the input signal voltage for freedom from grid current. A further increase of input causes rectification at the grid, with added damping of the grid input circuit, and a steady increase in distortion. An increase in the supply voltage raises the threshold point for grid current. Further data are available in Refs. 11, 12, 13, 14 and 15.

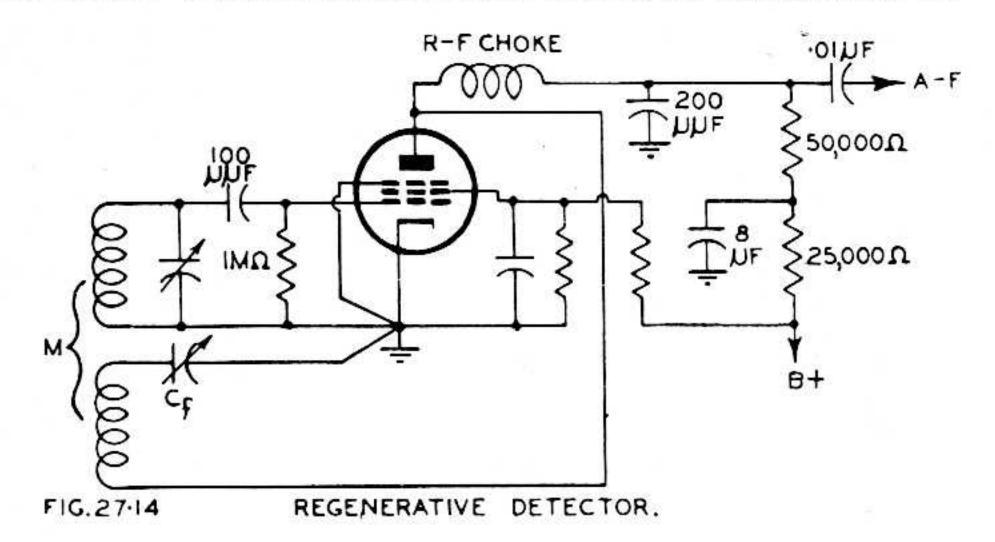

(E) Regenerative detectors

A common arrangement for this type of detector is shown in Fig. 27.14. amount of positive feedback is adjustable, by means of  $C_t$ , to allow increased sensitivity with various signal input voltages. Oscillation will occur when the degree of feedback is sufficiently large, and the circuit can then be used for the detection of CW telegraph signals. For battery operated valves it is usual to return the grid resistor to filament positive.

e

d

e

n

Best results are generally obtained using pentode valves and resistance-capacitance coupling to the following audio stage. This arrangement minimizes "threshold howl."

Feedback control is possible with a variety of circuits but least difficulty is usually experienced with the variable capacitor arrangement, or the use of a variable resistor in the screen circuit. The latter arrangement is advantageous as regards the reduction of detuning effects.

Further details of this type of detector can be found in Refs. 1, 5, 16, 17, 18, 19 and 20.

### (F) Superregenerative detectors

The superregenerative detector is a regenerative circuit in which the detector is automatically switched in and out of oscillation at a very low radio frequency rate (usually about 15 to 100 Kc/s). This switching frequency is called the "quenching" frequency. In general the quenching frequency is increased as the carrier frequency becomes greater, but sensitivity and selectivity are improved by using the lowest permissible value of quenching frequency. For many cases it is usual to make the quench frequency about twice the highest audio frequency contained in the modulation envelope, and it is not considered good practice for the quench frequency to be lower than this value. The amplitude of the quench voltage is also important and it will have a very appreciable effect on the selectivity characteristic. In general if the quench voltage amplitude is increased in a separately quenched circuit, the selectivity is reduced.

The advantage of this circuit is the extremely high sensitivity which is possible using a single valve. The disadvantages are the high noise level in the absence of a

signal, the poor selectivity, and the high distortion.

The circuit of Fig. 27.14 can be made to operate as a superregenerative detector by increasing the time constant of the grid resistance and capacitance combination, and making the amount of regeneration very large. The quenching frequency can be simply adjusted by altering the value of the grid resistance.

A separate quenching oscillator is often used with the regenerative detector arrangement, but as this requires additional circuit components and sometimes an additional valve, it is not so popular as the simple arrangement previously mentioned. The development of suitable types of double triode and converter valves largely overcomes

this objection, however, and many modern circuits use separate quenching.

Several other points of interest arise with this detector. Amplitude limiting occurs, so there is less interference from car ignition and similar noises than when other detectors are used; the output on strong signals is not much greater than for weak signals. Noise quieting and limiting are improved however, by using low quench frequencies. A r-f stage should be incorporated in receivers using this type of detector to reduce radiation. This additional stage will not materially alter the signal-to-noise ratio obtainable with the detector alone. Circuits incorporating the principle of superregeneration have been used in cheap F-M receivers; this point will receive some further consideration in the section on F-M receivers in Chapter 36.

The method to be adopted for measuring the selectivity of a superregenerative receiver requires some consideration. Conventional methods are usually inadequate since in most cases the problem is similar to that of taking the selectivity curve of a receiver having a.v.c., but in this case the a.v.c. cannot be disconnected. A suitable

procedure (Ref. 26) is as follows.

With no input signal applied the audio noise output is measured. A signal is applied at the resonance frequency and its amplitude adjusted until the noise is suppressed by about 10 to 20 db (or any convenient amount). The selectivity is then found by tuning the signal generator to various frequencies around resonance, in the usual manner, and the input voltage is adjusted until the same degree of quieting is obtained as at resonance. The difference between the two signal inputs off and at resonance for the same degree of quieting, gives the attenuation at the particular frequency being considered.

Further details of this detection system are available in Refs. 5 (page 662), 20 (page

148), 21, 22, 23, 24, 25 and 26.

### **SECTION 2: F-M DETECTORS**

(i) Types of detectors in general use (ii) General principles (iii) Phase discriminators (A) General (B) Design data (C) Design example (iv) Ratio detectors (A) General (B) Operation (C) Types of circuit (D) Design considerations (E) Practical circuits (F) Measurements on ratio detectors.

(i) Types of detectors in general use

Although many ingenious methods have been suggested for the detection of frequency modulated signals, only a few circuits have found general acceptance by receiver manufacturers. Of these detectors a form of locked oscillator (the Bradley detector) has been used by one large manufacturer, but does not appear to have been employed to any extent outside of this organization. Amplitude discriminators have been used to a very limited extent with duo-diode triode valves having a separate cathode for the two diodes. However, the generally accepted method of F-M detection has been the phase discriminator. A modification of the basic phase discriminator circuit has been used for the ratio detector, and this arrangement has achieved wide popularity because it allows a satisfactory F-M receiver to be constructed without the use of an additional amplitude limiting stage. Simple detuning of the signal circuits has been employed in one type of receiver (the Fremodyne) to give frequency to amplitude conversion, but this is only satisfactory in a very cheap receiver where cost is more important than quality.

In what follows attention will be confined, mainly, to the design procedures to be adopted for phase discriminators and ratio detectors. References are listed at the end of this chapter, and can be consulted for details of a number of the alternative detection systems available. The amplitude and phase discriminators used in connection with Automatic Frequency Control Systems are further considered in Chapter 29.

(ii) General principles

The circuits which will be considered here utilize tuned circuits to convert frequency changes to amplitude changes. The amplitude modulated carrier is then applied to detectors (usually diodes) to recover the intelligence contained in the received signals.

Although the amplitude modulated carrier applied to the detectors is also frequency modulated, the detectors are only sensitive to amplitude changes, and so it is only the resultant amplitude variations which appear at the output of the detector stage. It is because the detectors are sensitive to amplitude changes, that some method of limiting

The tuned circuits to be described are called discriminators, although this name is often taken to include the diode detectors as well. If distortion is not to be introduced by the discriminator it is essential that the amplitude variations produced be directly proportional to the frequency variations i.e. the circuit must be linear over the full range of applied frequency deviation. The usual precautions for reducing distortion in the detector circuits must also be applied, just as for any other A-M detector. These precautions have been discussed previously, and those given for diode detectors should be carefully observed here. One big advantage does appear, however, the percentage amplitude modulation is likely to be quite small, depending on the frequency-amplitude conversion efficiency of the discriminator circuit, and so the possibility of non-linear distortion is considerably reduced.

# (iii) Phase discriminators

(A) General

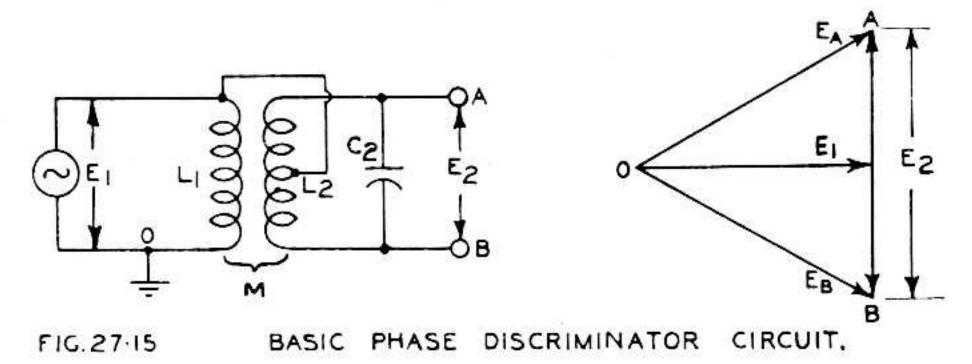

The basic circuit arrangement, together with the voltage distribution at the resonant frequency, for a phase discriminator is shown in Fig. 27.15. The name arises because the operation is dependent on the  $90^{\circ}$  phase shift which occurs at resonance between the primary and secondary voltages of a tuned transformer. When the frequency of the applied primary voltage  $\mathbf{E}_1$  (the magnitude of this voltage will be

assumed constant for the moment) alters, the phase angle between  $E_1$  and  $E_2$  changes from that at resonance. This leads to a change in the relative magnitudes of  $E_A$  and  $E_B$ .

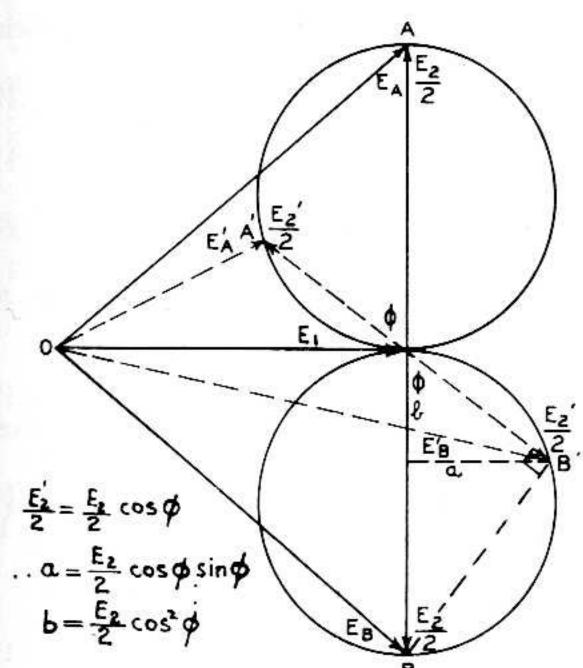

The vector relationship between the primary and half secondary voltages, for the phase discriminator, are shown in Fig. 27.16. This assumes constant primary voltage  $\mathbf{E}_1$ .

FIG.27-16 VOLTAGE RELATIONSHIPS IN PHASE DISCRIMINATOR WITH CONSTANT PRIMARY VOLTAGE.

If the primary voltage  $E_1$  has its amplitude varied in a suitable manner (e.g. by setting the coupling between the transformer windings, for given primary and secondary Q's, so that two primary voltage humps of the required amplitude appear as the frequency is varied) the linearity and sensitivity of the discriminator can be very appreciably improved.

This statement, regarding linearity and sensitivity, refers, of course, to the relationship between voltage output and frequency-deviation from the central reference frequency (i.e. the nominal intermediate frequency).

Analysis of the phase discriminator for F-M applications has been made by K. R. Sturley (Refs. 27 and 28), and the results of this analysis will be used below It might be mentioned that a number

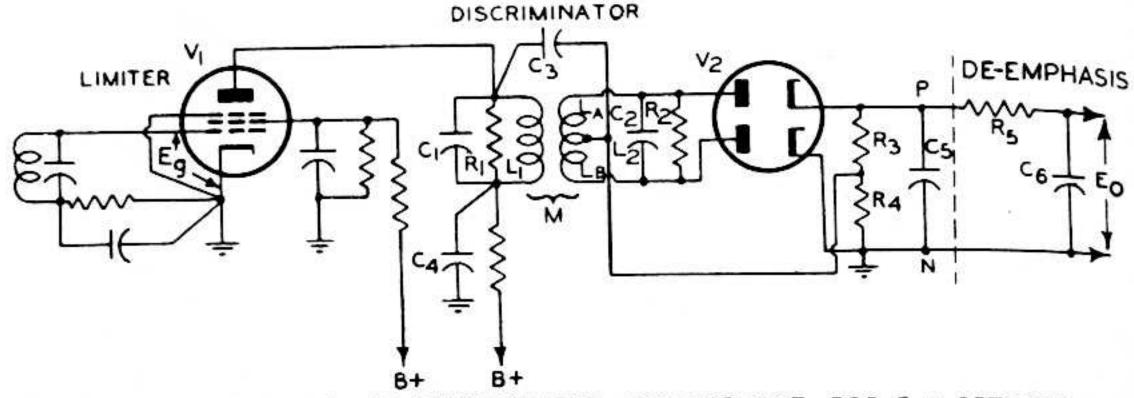

of discriminator circuits for a wide variety of applications have been designed using the data derived by Sturley and very satisfactory results have been obtained in practice. Before proceeding to set out the design data, the circuit of Fig. 27.17 will be briefly discussed.

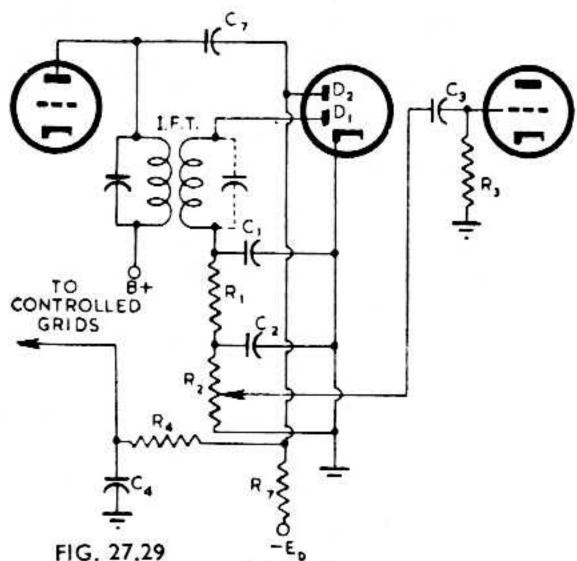

The voltages applied to the plates of the double diode valve  $V_2$  will be  $E'_A$  and  $E'_B$  respectively. The output voltages from the diodes are developed across  $R_3$  and  $R_4$ , and the circuit is arranged so that the available output voltage is equal to the **difference** between the two separate voltages. This means that when the frequency of the carrier voltage is exactly equal to the intermediate frequency, no output will be obtained from the detector. Reference to Fig. 27.16 should help to make this point quite clear, since the rectified voltages across  $R_3$  and  $R_4$  in Fig. 27.17 are given by the peak voltages applied to the diode plates multiplied by the detection efficiency of the diodes. As the signal deviates from the central reference frequency (i.e. the intermediate frequency), a voltage  $(E_{out})$  will appear between the points P and N (Fig. 27.17), and its polarity will depend on the relative magnitudes of the voltages across  $R_3$  and  $R_4$ ; e.g. point P will be negative with respect to point N when the voltage across  $R_3$  is less than that across  $R_4$ . It follows that it should be possible to calculate

FIG 27-17

TYPICAL PHASE DISCRIMINATOR ARRANGEMENT FOR F-M DETECTION.

the relationship between output voltage and frequency change from

$$E_{out} = \eta(E'_A - E'_B) \tag{11}$$

where  $\eta$  = the diode detection efficiency, and is assumed to be the same for both diodes of  $V_2$ .

### (B) Design data

For most designs it is usual to take the total secondary voltage  $E_2$  as being twice the primary voltage  $E_1$  i.e.

$$E_2/E_1 = 2.$$

(12)

Primary and secondary Q's are made equal, so that

$$Q = Q_1 = Q_2. ag{13}$$

The value for Q is determined from

$$Q = f_r/(2\Delta f) \tag{14}$$

where  $f_r$  = intermediate frequency

and  $2\Delta f$  = total frequency range for which substantially linear operation is required.

The coefficient of coupling for the transformer is found from

$$Qk = 1.5 (15)$$

when a good compromise between sensitivity and linearity is required (the usual case).

For special cases where linearity is the main requirement it is suggested that

$$Qk = 2$$

(16)

be used. The loss in sensitivity in this case is about 1.54 times as can be seen by comparing eqns. (20) and (21).

From the principles of coupled circuits it is possible to show that

$$\frac{E_2}{E_1} = Q_2 k \sqrt{\frac{L_2}{L_1}} \tag{17}$$

and for our particular cases with  $E_2/E_1=2$  and Qk=1.5 or 2, the relationship between  $L_2$  and  $L_1$  is

$$L_2/L_1 = 1.77 \text{ (for } Qk = 1.5)$$

(18)

and

$$L_2/L_1 = 1$$

(for  $Qk = 2$ ).

(19)The discriminator sensitivity at  $f_r$  is given by

$$S_{(Qk = 1.5)} = 5.465 \times 10^3 g_m Q^2 L_1 \eta E_g$$

volts per kilocycle deviation, (20)

$\overline{S}_{(Qk=2)} = 3.554 \times 10^3 g_m Q^2 L_1 \eta E_q$  volts per kilocycle deviation, (21)

where

$g_m$  = mutual conductance of  $V_1$ Q = magnification factor determined from eqn. (14)

$L_1$  = primary inductance of transformer

$\eta$  = diode detection efficiency

$E_q$  = peak voltage between grid and cathode of  $V_1$ . and

It should be apparent that the sensitivity, given by eqns. (20) and (21), is directly proportional to  $E_g$  and so the output from the discriminator is dependent on the input voltage. To overcome this difficulty the valve V<sub>1</sub> is arranged as a limiter in such a way that the product  $g_m E_g$  is kept almost constant, and thus the output voltage is no longer directly dependent on the magnitude of the signal input voltage.

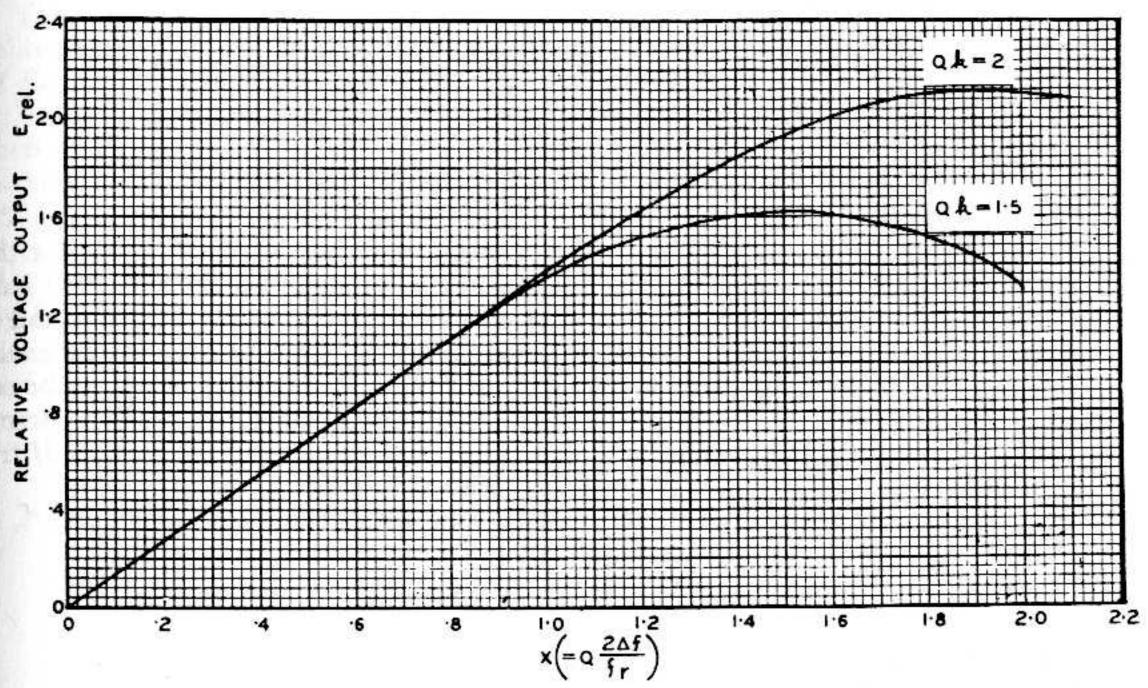

Curves of discriminator output voltage versus frequency deviation can be found from vector diagrams similar to that of Fig. 27.16, and then introducing suitable correction factors to allow for variations in  $E_1$  deliberately introduced by the transformer design. However, it is possible to determine two generalised curves for the design conditions previously imposed, one curve for Qk = 1.5 and the other for Qk = 2. The curves are shown in Fig. 27.18A, and relate the quantity X (which is a function of bandwidth) to the relative output voltage  $E_{rel}$ . Only the positive halves of the curves are shown since the negative halves have substantially the same shape. To determine the output voltage  $E_{out}$  against frequency, it is only necessary to multiply the horizontal scale by a factor determined by eqn. (14), and the vertical scale by a factor determined by eqn. (20) or eqn. (21) (depending on whether Qk = 1.5 or 2 is used).

FIG. 27-18(A) GENERALISED PHASE DISCRIMINATOR CURVES OF RELATIVE VOLTAGE OUTPUT (Erel.) VERSUS X WITH E2/E1=2; Q4=1-5 AND 2.

The two curves shown in Fig. 27.18(A) are calculated from the following equations. For Qk = 1.5, the relative voltage output is

$$E_{rel} = \frac{3.25A}{\sqrt{(3.25 - X^2)^2 + 4X^2}}$$

(22)

and for Qk = 2,

$$E_{rel} = \frac{5A}{\sqrt{(5 - X^2)^2 + 4X^2}}$$

(23)

where

$$A = \sqrt{1 + X^2} \left[ \sqrt{\left(1 + \frac{X}{1 + X^2}\right)^2 + \left(\frac{1}{1 + X^2}\right)^2} - \frac{1}{1 + X^2} \right]^2$$

$$\sqrt{\left(1-\frac{X}{1+X^2}\right)^2+\left(\frac{1}{1+X^2}\right)^2}$$

$X = Q 2\Delta f/f_r$

Q = magnification factor determined from eqn. (14). Equation (14) is the condition for X = 1

$\Delta f$  = frequency deviation from  $f_r$

and  $f_r$  = intermediate frequency.

To illustrate the design procedure, and to bring out additional points, a worked example is appended.

(C) Design example

A phase discriminator is required for use with a 10.7 Mc/s F-M i-f channel. The maximum frequency deviation of the carrier is ± 75 Kc/s. To make the problem

complete it will be taken that the highest audio frequency is 15 Kc/s and the deemphasis time constant is 75 micro-seconds.

(a) The majority of applications call for reasonable discriminator sensitivity and so the condition Qk = 1.5 (see eqn. 15) is practically always used. Also, high primary dynamic impedance will increase the sensitivity of the discriminator. However, since Q is fixed by other considerations (see eqn. 14)  $L_1$  should be large, but  $L_1$  is limited by  $L_2$  which in turn is limited by the permissible minimum secondary capacitance  $C_2$ . A value is selected for  $C_2$  and the design can then proceed.

(b) A suitable value for  $C_2$ , including all strays, is 50  $\mu\mu$ F. Then

$$L_2 = \frac{25\ 330}{10.7^2\ \times\ 50} = 4.41\ \mu\text{H}.$$

From eqn. (18),

$$L_1 = \frac{L_2}{1.77} = \frac{4.41}{1.77} = 2.5 \ \mu H.$$

From this

$$C_1 = \frac{25\ 330}{10.7^2\ \times\ 2.5} = 88.5\ \mu\mu\text{F}$$

(including all strays).

(c) If the discriminator frequency—voltage characteristic were exactly linear then it would be sufficient to make the total frequency range  $2\Delta f = 2 \times 75 = 150 \text{ Kc/s}$ . To this would be added an allowance for frequency drift due to the oscillator and the discriminator tuned circuits. Since the discriminator characteristic is not exactly linear (it is linear for about 80% of the total curve using the data given as can be seen from Fig. 27.18) and the frequency drift is not always small it has become common practice in broadcast F-M circuits (of the type being considered) to make  $2\Delta f$  from 200 to 400 Kc/s.

As a practical compromise we will take the total bandwidth  $(2\Delta f)$  as 250 Kc/s, but the design procedure is the same irrespective of what bandwidth is selected.

With  $2\Delta f = 250$  Kc/s we have from eqn. (14)

$$Q = 10.7/0.25 = 42.8.$$

From eqn. (15), Qk = 1.5

and so k = 1.5/42.8 = 0.035.

(d) Summarizing, for the discriminator transformer (see also Fig. 27.17)

$L_1=2.5~\mu\mathrm{H}$ ;  $L_2=4.41~\mu\mathrm{H}$ ;  $C_1=88.5~\mu\mu\mathrm{F}$ ;  $C_2=50~\mu\mu\mathrm{F}$ ;  $Q=Q_1=Q_2=42.8$ ; k=0.035;  $M=0.116~\mu\mathrm{H}$ . Secondary winding to be centre-tapped. The capacitance values include all strays.

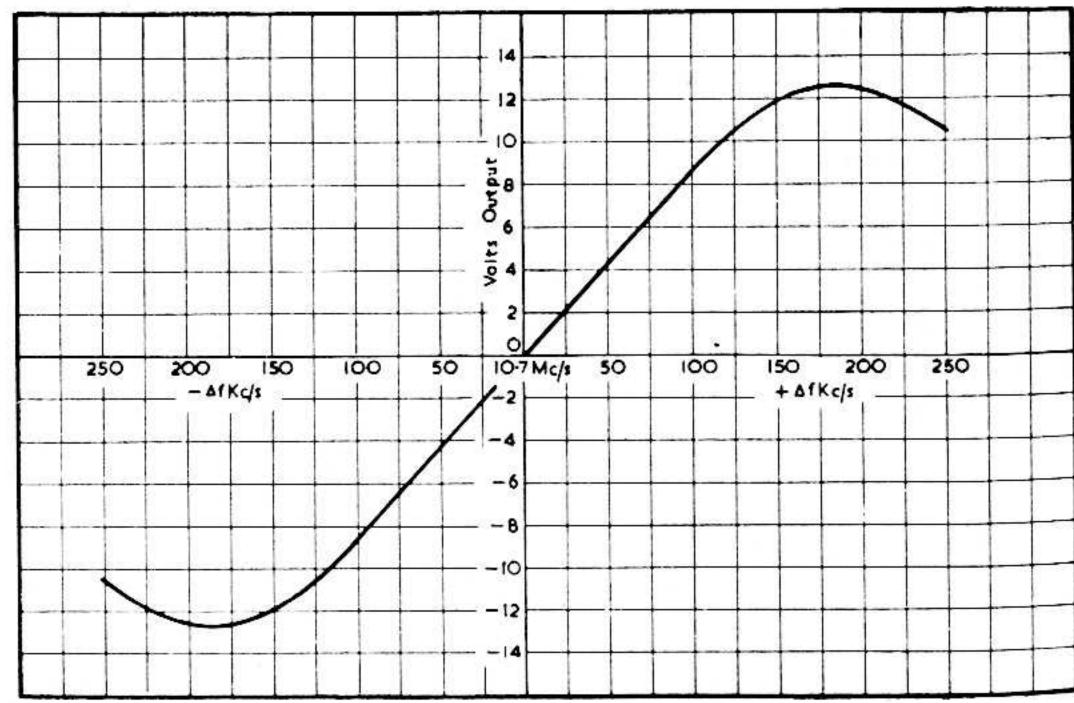

FIG. 27.18(B) Discriminator Characteristic Obtained From Design Example

(e) The discriminator sensitivity at  $f_r$  is given by eqn. (20). Assume Eg=1 volt (peak),  $g_m=5$  mA/volt and  $\eta=0.7$ . Then

$S(Qk = 1.5) = 5.465 \times 10^3 \times 5 \times 10^{-3} \times 42.8^2 \times 2.5 \times 10^{-6} \times 0.7 \times 1$ = 0.0875 volts per kilocycle deviation.

This also allows the vertical scale factor to be determined for the complete discriminator curve as shown on Fig. 27.18(B). The horizontal scale factor is found from

$$X=Q~rac{2\Delta f}{f_r}=1$$

[i.e. eqn. (14)]. Therefore  $\Delta f=rac{Xf_r}{2Q}=rac{10.7~ imes~10^3}{2~ imes~42.8}=125~{

m Kc/s}.$

The procedure for finding the plotted points on the curve of Fig. 27.18(B) is as follows. Draw up a table, as shown below, with values of X corresponding to values of  $E_{rel}$  read from the curve of Fig. 27.18(A). Since it has just been determined that  $\Delta f = 125 \text{ Kc/s}$  when X = 1, the column for  $\Delta f$  can be filled in (e.g. when X = 0.8 then  $\Delta f = 125 \times 0.8 = 100 \text{ Kc/s}$ , and so on). The sensitivity has been determined as 0.0875 volts per kilocycle deviation, and so for 25 Kc/s deviation  $E_{out} = 0.0875 \times 25 = 2.19$  volts (the lowest deviation frequency in the table should be used to find  $E_{out}$  in this case). It is now seen that the value of  $E_{out} = 2.19$  volts corresponds to  $E_{rel} = 0.28$ , and so the scale factor is 2.19/0.28 = 7.82. If 7.82 is now multiplied by  $E_{rel}$  in each case, the column for  $E_{out}$  can be filled in. The complete curve for  $E_{out}$  versus  $\Delta f$  can now be plotted.

| $\boldsymbol{X}$ | $\Delta f$ | $E_{rel}$ | E out |

|------------------|------------|-----------|-------|

| 0.2              | 25         | 0.28      | 2.19  |

| 0.4              | 50         | 0.56      | 4.38  |

| 0.6              | 75         | 0.84      | 6.56  |

| 0.8              | 100        | 1.12      | 8.76  |

| 1.0              | 125        | 1.36      | 10.61 |

| 1.2              | 150        | 1.52      | 11.9  |

| 1.4              | 175        | 1.6       | 12.5  |

| 1.5              | 187.5      | 1.62      | 12.7  |

| 1.6              | 200        | 1.6       | 12.5  |

| 1.8              | 225        | 1.52      | 11.9  |

| 2.0              | 250        | 1.31      | 10.5  |

(f) It now remains to determine suitable values for the other components in the circuit of Fig. 27.17.

$C_3$  is for the purpose of connecting the transformer primary to the secondary centre-tap, and providing isolation of the secondary from the h.t. on the plate of  $V_1$ . A suitable value is  $100~\mu\mu F$ . The capacitor should have high insulation resistance.

$C_4$  is a by-pass capacitor; a value of about 0.01  $\mu$ F is usual.

$R_3$  and  $R_4$  are made equal, and are generally about 100 000 ohms each.

$C_5$  acts as a by-pass for i-f but must not appreciably affect the audio frequency

response. The usual value is about 100  $\mu\mu$ F.

The de-emphasis network consists of  $R_5$  and  $C_6$ . For 75 microsecond de-emphasis the nominal values would be 75 000 ohms and 0.001  $\mu$ F respectively. If an improved a.c./d.c. ratio is thought to be necessary then suitable values would be say, 0.25 M $\Omega$  and 300  $\mu\mu$ F. The grid resistor in the following a-f stage should not be less than 1 M $\Omega$  if excessive loss in gain is to be avoided. However, the actual values used in a receiver will generally deviate from these nominal figures if the overall audio frequency response of the receiver is made to follow the 75 microsecond de-emphasis curve to 15 Kc/s, because of the presence of stray capacitances etc. and in some cases to help compensate for the overall a-f response.

To determine  $R_1$ :—the transformer primary damping due to a single diode circuit, connected as shown, is  $R_{dc}/3$ . For this circuit  $R_{dc} = R_3 = R_4 = 100\,000$  ohms.

Also, because of the circuit arrangement,  $R_3$  and  $R_4$  are in parallel. The total damping, due to diode conduction currents in addition to  $R_3$  and  $R_4$ , is then

$$\frac{1}{2}\left(\frac{R_{dc}}{3}\right) = \frac{100\ 000}{6} = 16\ 600\ \Omega.$$

If  $R_3$  is not equal to  $R_4$ , the damping resistance is given by  $R_3/3$  and  $R_4/3$  in parallel i.e.

$$R_3R_4/3(R_3+R_4)$$

. (When  $R_3=R_4=R_{dc}$  the value  $R_{dc}/6$  is obtained as above).

Take the undamped primary Q (written as  $Q_u$ ) as being 100, and neglect the additional damping due to the plate resistance of  $V_1$ . Then the total damping resistance (R) required to obtain a primary Q of 42.8 is

$$R = \frac{Q_u Q \omega L_1}{Q_u - Q} = \frac{100 \times 42.8 \times 2\pi \times 10.7 \times 2.5}{100 - 42.8}$$

$$= 12,500 \ \Omega.$$

From this

$$R_1 = \frac{12\,500\,\times\,16\,600}{(16\,600\,-\,12\,500)} = 50\,600\,\Omega.$$

To determine  $R_2$ : The transformer secondary damping is given by  $R_3 = R_4 = R_{dc} = 100\,000\,\Omega$ .

(This follows because the damping across each half of the secondary is  $R_3/2$  and  $R_4/2$  respectively, and in each case there is a step up, due to the transformer being centre tapped, of 4 times. From this, across the whole of the transformer secondary there are two resistances  $4R_3/2$  and  $4R_4/2$  in parallel, and since  $R_3 = R_4 = R_{dc}$  the above result is obtained immediately).

The total damping resistance (R') required to make  $Q_2 = Q_1 = 42.8$  is

$$R' = 12500 \times 1.77 = 22100 \Omega$$

.

From this

$$R_2 = \frac{22\ 100\ \times\ 100\ 000}{(100\ 000\ -\ 22\ 100)} =\ 28\ 400\ \Omega.$$

The design of the limiter stage will be discussed in Chapter 29.

(g) Some causes of discriminator unbalance will be mentioned, before leaving this section, and it is helpful to consider the circuit as a bridge in which unbalance has to be eliminated. Even when the transformer secondary is centre-tapped accurately, unbalance can occur because the capacitive coupling between the two halves of the secondary winding and the primary winding is not necessarily equal. This calls for care in the method of arranging the windings. Two methods are in common use. The first uses a bifilar method with the two halves of the secondary wound side by side. The second method arranges the secondary into two halves, placed on either side of the primary winding, and the coupling of both sections, including that due to stray capacitances, is made equal.

Capacitive unbalance will also occur when the input capacitances of the diodes are not equal. Suitable arrangement of stray capacitances can often be used to help in offsetting this effect.

The use of a small capacitance connected across one of the diodes is helpful in reducing capacitive unbalance effects.

Balancing of the conduction resistances of the two diode units is largely outside the control of the receiver designer, but variation in the value of  $R_3$  and  $R_4$  can be made to assist in cases where a very high degree of balance is thought to be necessary. Additional precautions of this nature are seldom carried out in commercial receivers.

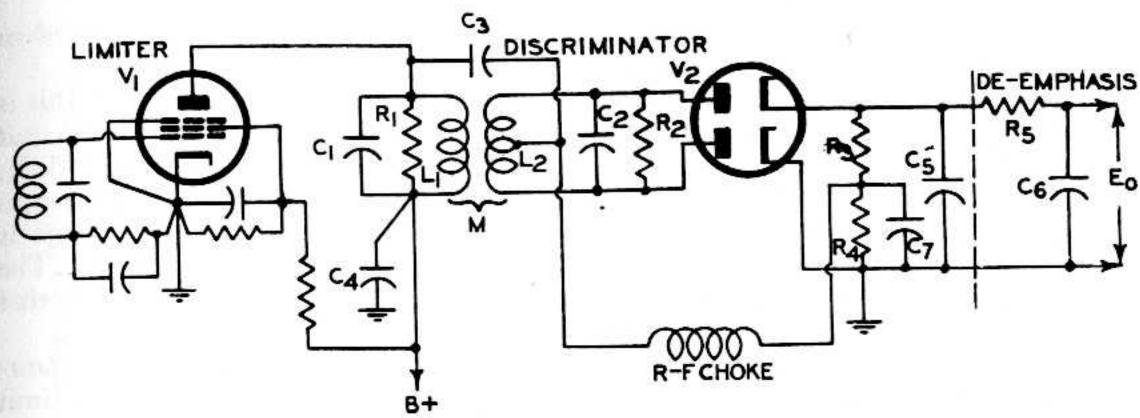

It should be noted in Fig. 27.17 that, if the resistors  $R_3$  and  $R_4$  are shunted by two separate capacitors, an additional series resistor or r-f choke will be required between the junction of  $R_3$  and  $R_4$  and the centre tap on  $L_2$ . Connecting the junction of  $R_3$  and  $R_4$  through a by-pass capacitor to ground would also effectively short-circuit the i-f primary voltage to ground, if the additional component is not used. For most circuits the arrangement shown is applicable, since it requires a minimum of components consistent with satisfactory performance. The alternative arrangement

FIG. 27-19 ALTERNATIVE ARRANGEMENT FOR PHASE DISCRIMINATOR.

is shown in Fig. 27.19. The design procedure to be used is exactly as before, except that the primary circuit damping due to the diode circuits (the damping is actually across the r-f choke) will be approximately  $R_{dc}/4$  instead of  $R_{dc}/6$ ; the secondary circuit damping is  $R_{dc}$  as previously, where  $R_{dc} = R_3 = R_4$ . If a resistor is substituted for the r-f choke then the circuit damping is again modified depending on the value of resistance used in the circuit. Considerations leading to the choice of a suitable value for the inductance of the r-f choke will be given in detail in Chapter 29 Sect. 2, in connection with the discussion on a.f.c. discriminators.

It is perhaps worth mentioning that hum due to heater-cathode leakage is sometimes troublesome in discriminator circuits, particularly with miniature diodes, and a simple and effective cure for this trouble is to make the cathode positive with respect to the heater. This can be readily effected, for example in Fig. 27.19, by connecting a 10 000  $\Omega$  resistor by-passed by, say, a 0.01  $\mu$ F mica capacitor between the earthy end of  $R_4$  and ground; the junction of  $R_4$  and the 10 000  $\Omega$  resistor is then connected to B+ via a series resistor whose value is selected so that about 10 to 15 volts appears across the 10 000  $\Omega$  resistor (which now forms one arm of a voltage divider). In a typical case the series resistor would be about 0.16 M $\Omega$  for a B+ of 250 volts.

### (iv) Ratio detectors

#### (A) General

Many of the details given below, regarding ratio detectors, have been taken from Refs. 34, 35 and 36. Practical experience with several of the arrangements shown has confirmed much of the data given in the design sections. However, a number of additional factors will warrant discussion.

The principle underlying many circuits for F-M detection is the peak rectification of two i-f voltages, the relative amplitudes of which are a function of frequency, together with means for combining the rectified voltages in reversed polarity. The output is then equal to the difference between the two rectified voltages. This statement is directly applicable to the phase discriminator circuits of Figs. 27.17 and 27.19, the two i-f voltages being those applied to the diode plates, and the rectified voltages combined in reversed polarity being those which appear across the load resistors  $R_3$  and  $R_4$ . The way in which the two i-f voltages, applied to the diode plates, are dependent on the instantaneous intermediate frequency has been discussed in connection with Figs. 27.15 and 27.16. It was mentioned previously that, with the phase discriminator, changes in the magnitude of the input signal will give rise to amplitude changes in the resultant output voltage, and the need for some form of amplitude limiting was emphasized.

In an attempt to eliminate the necessity for a limiter, a ratio type of detector has been developed from the basic phase discriminator circuit. In this modified circuit the rectified voltages are split into two parts in such a way that their ratio is proportional to the ratio of the instantaneous i-f voltages applied to the detector diodes, and the sum of the two rectified voltages is kept constant. It has been found in this type of circuit that the useful output voltage, which is proportional to the difference between the two rectified voltages developed by the diode detectors, tends to be independent

of amplitude variations superimposed on a frequency modulated voltage applied to the discriminator circuit input terminals.

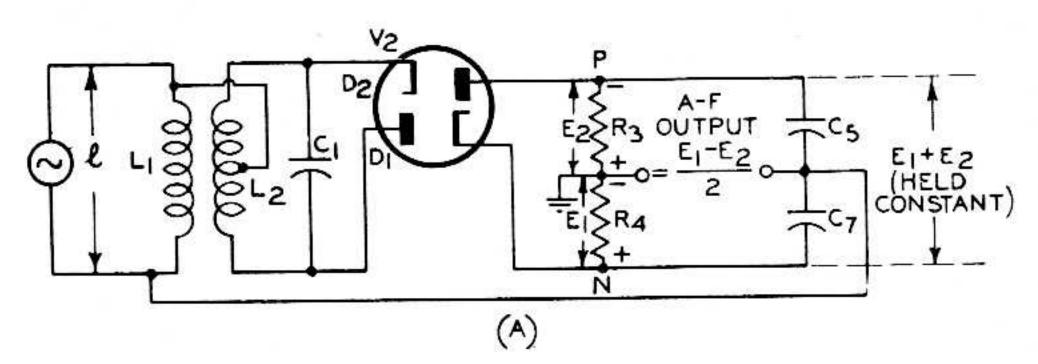

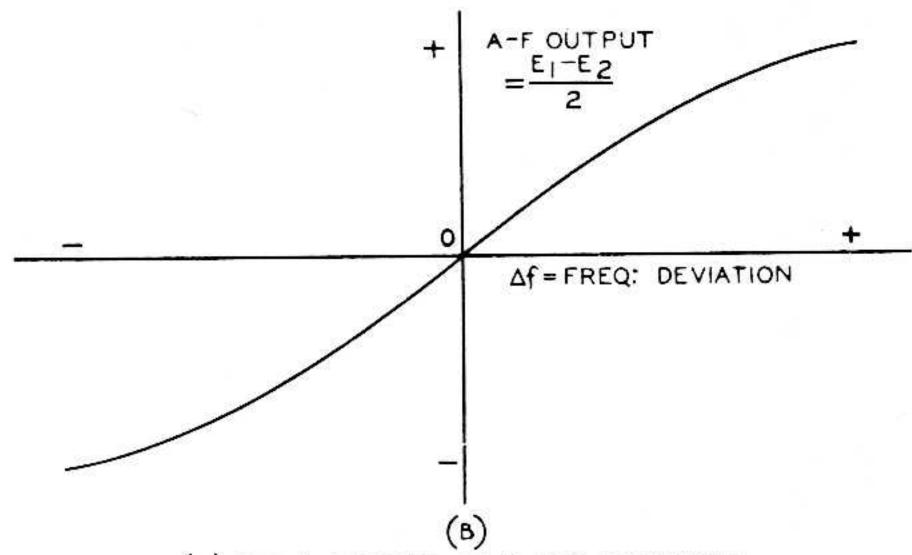

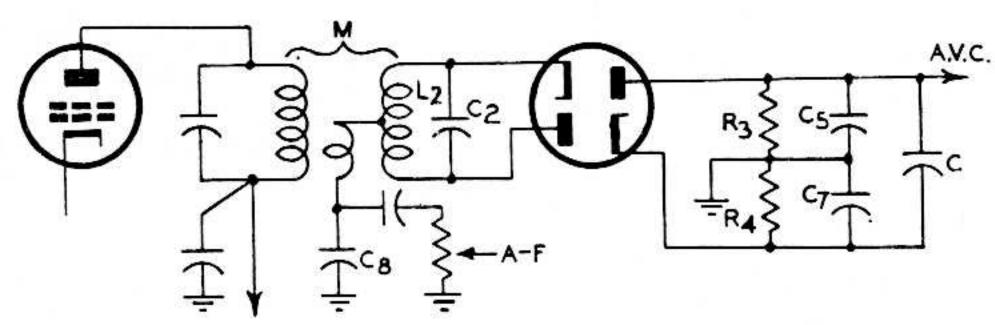

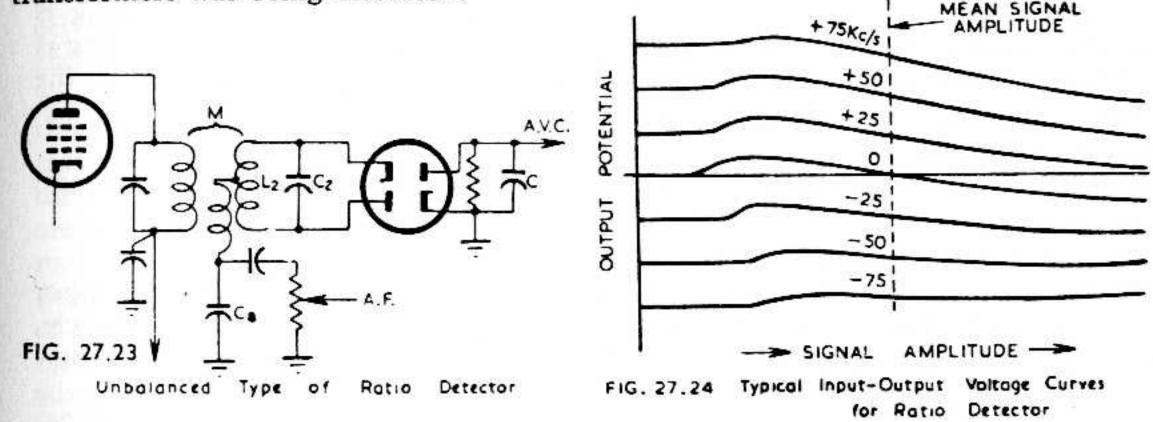

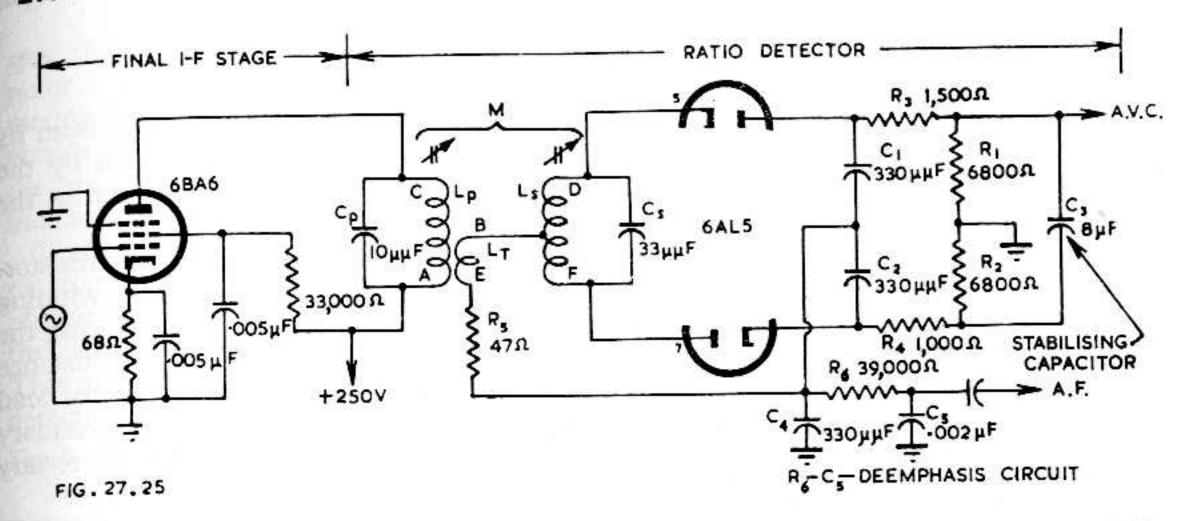

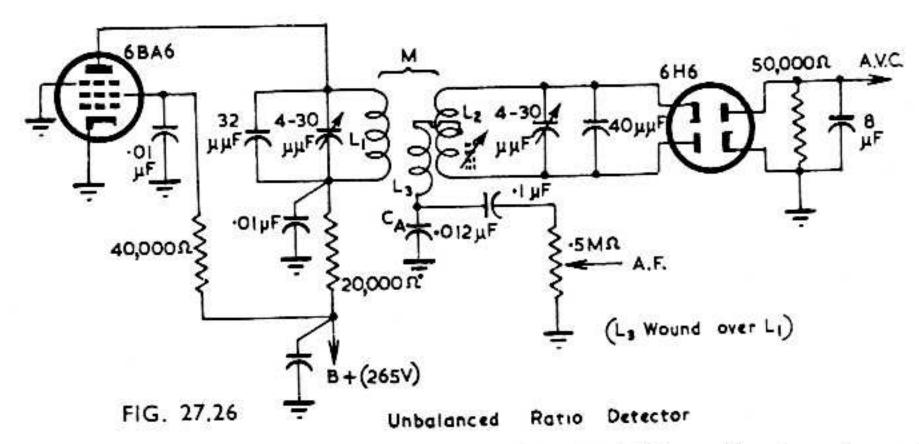

A basic ratio detector circuit is shown in Fig. 27.20(A). It can be seen that this is similar to the conventional phase discriminator but one of the diodes is reversed, and so the total voltage between the points P and N is equal to the sum of  $E_1$  and  $E_2$ . The sum of  $E_1$  and  $E_2$  is held constant by means of a battery or a large capacitance. This point will be further discussed as we proceed. The audio output voltage is taken from the junction of  $R_3$ ,  $R_4$  and  $C_5$ ,  $C_7$  and is equal to  $(E_1 - E_2)/2$ . The voltage output with frequency change is seen from Fig. 27.20(B) to be similar to that for a conventional discriminator circuit.

The sum voltage  $(E_1 + E_2)$  can be stabilized by using either a battery or by shunting a large capacitance across the load resistors  $R_3$  and  $R_4$ . A battery would limit the operation in such a way that the input signal would need to be at least strong enough to overcome the fixed bias due to the battery voltage. A better solution is to use a capacitor, since the voltage across it will vary in proportion to the average signal amplitude and thus automatically adjust itself to the optimum operating level. This allows amplitude rejection to be secured for a wide range of input signal voltages, the lowest useful signal being determined by the ability of the diode rectifiers to conduct with small input voltages.

When a capacitor is used to stabilize the rectified output voltage its capacitance must be sufficiently large so that the sum of  $E_1 + E_2$  cannot vary at an audio frequency rate. This calls for a time constant in the circuit made up from  $R_3$ ,  $R_4$  and the additional capacitance C of about 0.2 seconds. The effects of  $C_5$  and  $C_7$  on the time constant can be neglected, since the value of the capacitance C will be of the order of microfarads (usually about  $8\mu F$ ).

FIG.27-20 (A) BASIC CIRCUIT OF RATIO DETECTOR.

(B) TYPICAL OUTPUT CURVE.

FIG. 27-21 RATIO DETECTOR CIRCUIT SHOWING CONDITIONS FOR DIFFERENT SIGNAL INPUT VOLTAGES.

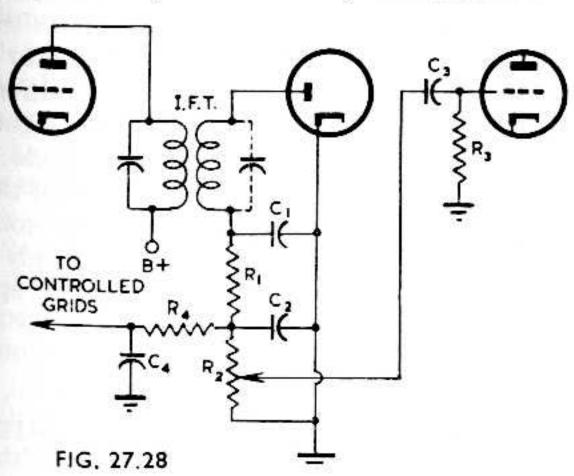

It is worth noting that the a.v.c. voltages available from ratio detector circuits have values which are not always directly suitable for application to controlled stages. Some form of voltage divider arrangement is often necessary to obtain suitable voltages for securing the desired a.v.c. characteristic.

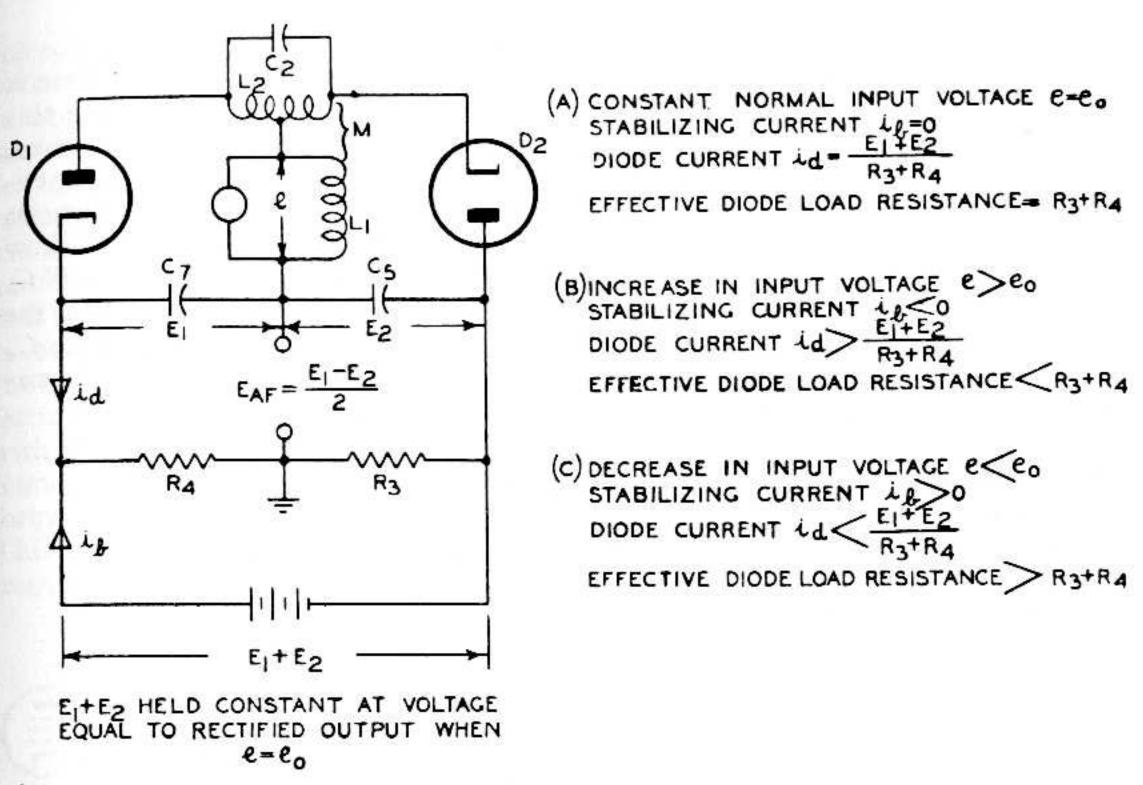

#### (B) Operation

A brief qualitative description of the operation of the ratio detector will be given here. A complete quantitative analysis has not been made, although many of the significant factors have been investigated (see Refs. 34, 35 and 36).